SPI Interface 185 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

The SPI rate may be calculated as: PCLK rate / SPCCR value. The pclk rate is CCLK / VPB divider rate as determined by the

VPBDIV register contents.

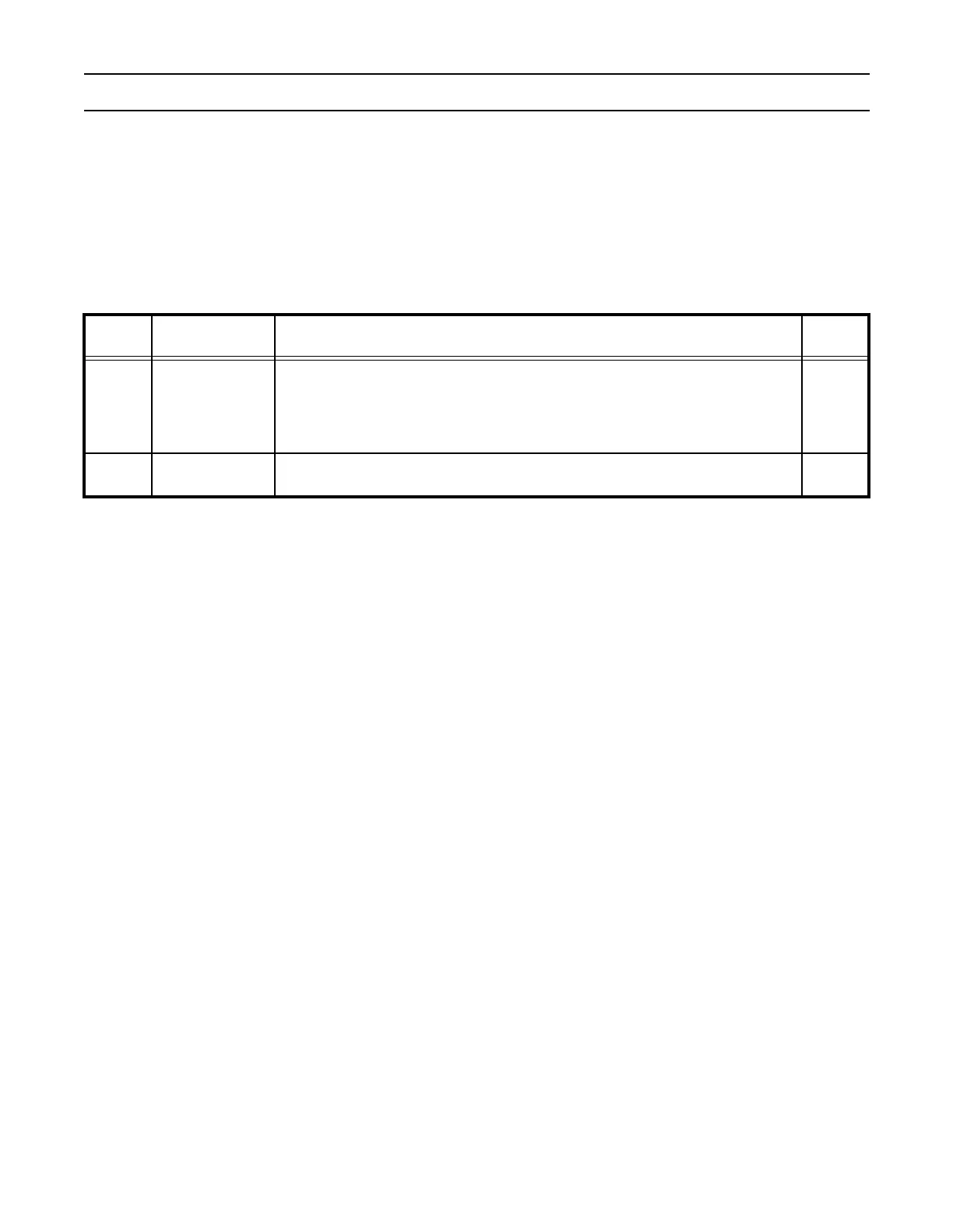

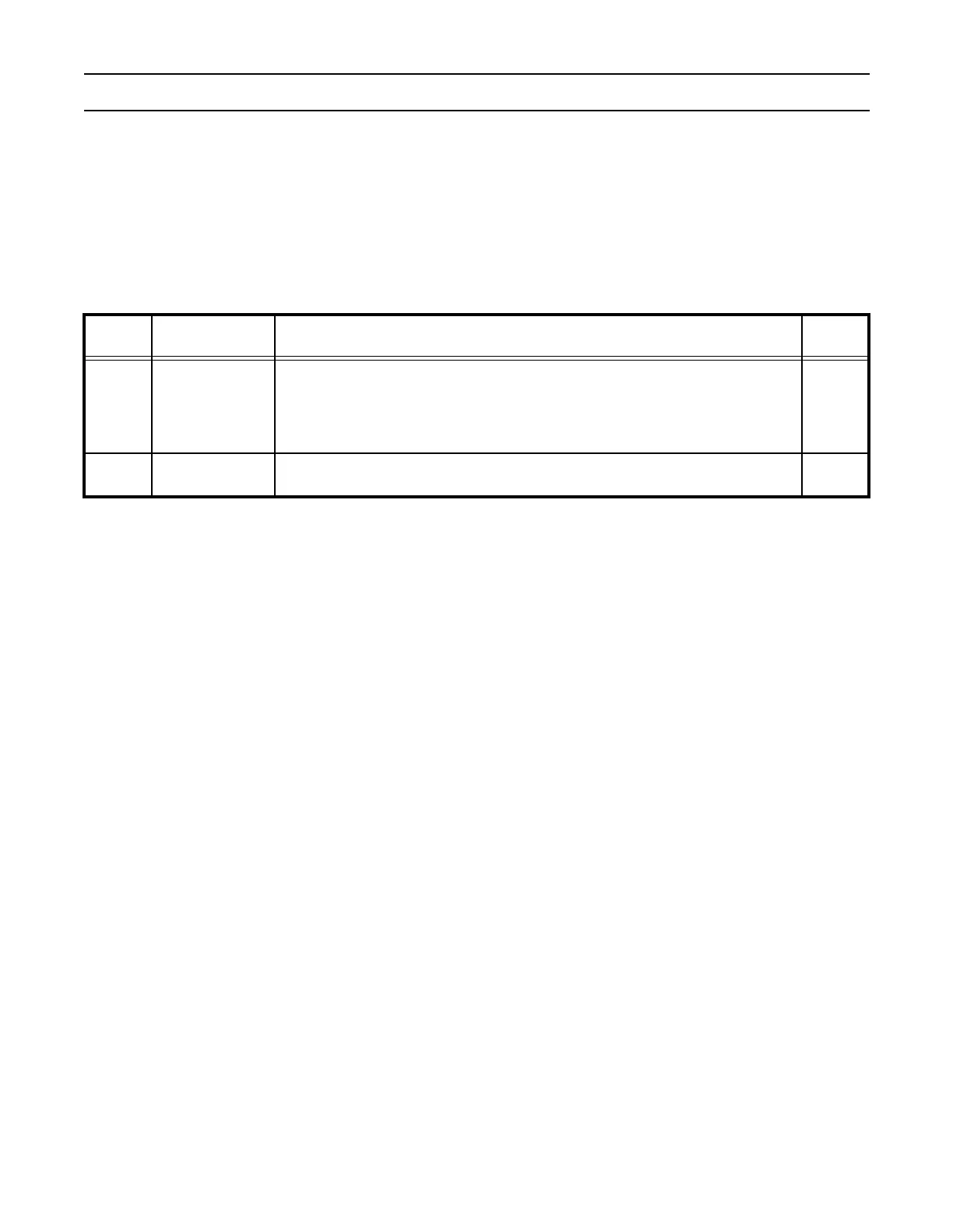

SPI Interrupt Register (S0SPINT - 0xE002001C, S1SPINT - 0xE003001C)

This register contains the interrupt flag for the SPI interface.

Table 120: SPI Interrupt Register (S0SPINT - 0xE002001C, S1SPINT - 0xE003001C)

SPINT Function Description

Reset

Value

0 SPI Interrupt

SPI interrupt flag. Set by the SPI interface to generate an interrupt. Cleared by writing

a 1 to this bit.

Note: this bit will be set once when SPIE=1 and at least one of SPIF and WCOL bits

is 1. However, only when SPI Interrupt bit is set and SPI Interrupt is enabled in the

VIC, SPI based interrupt can be processed by interrupt handling software.

0

7:1 Reserved

Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

Loading...

Loading...