Introduction 22 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

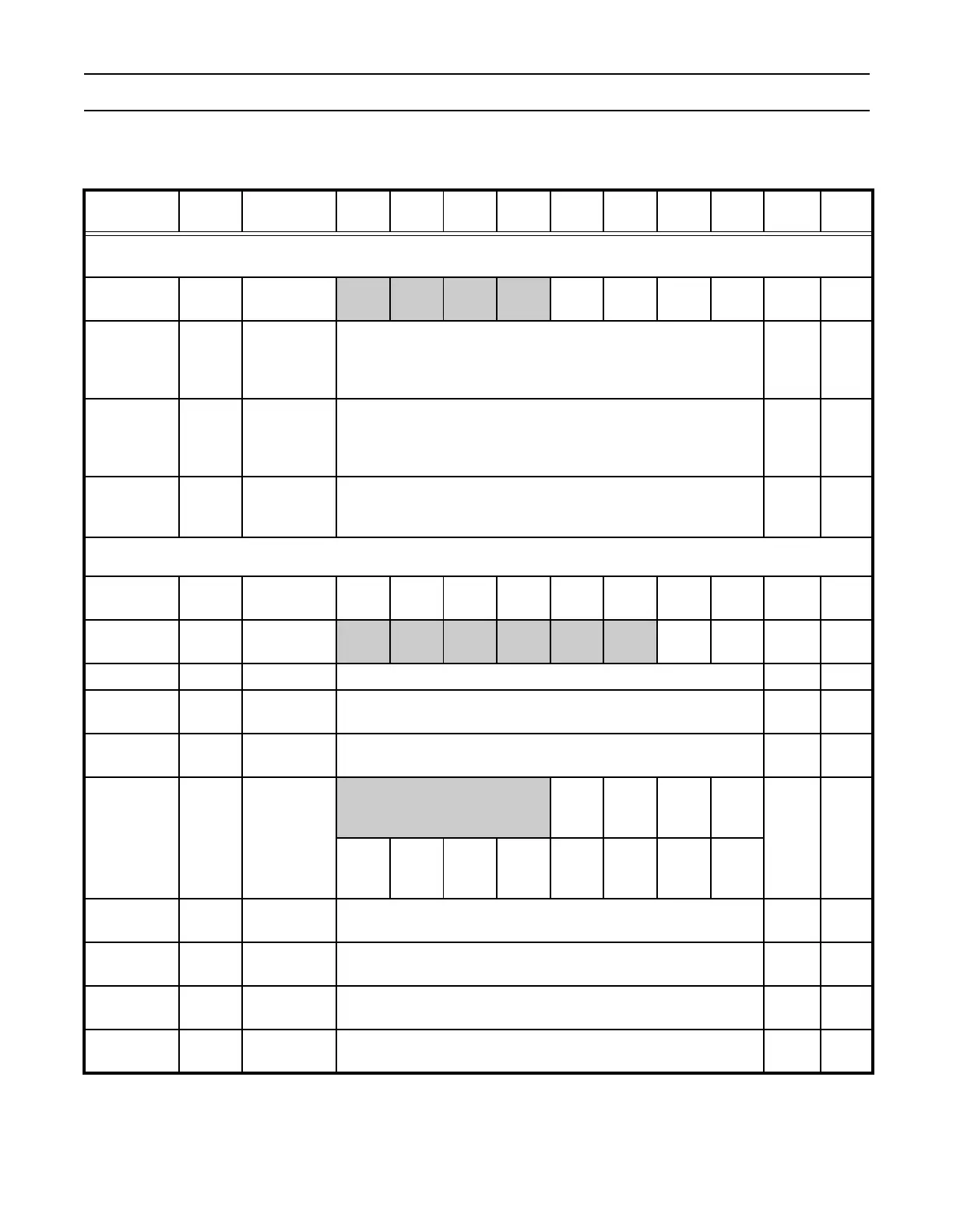

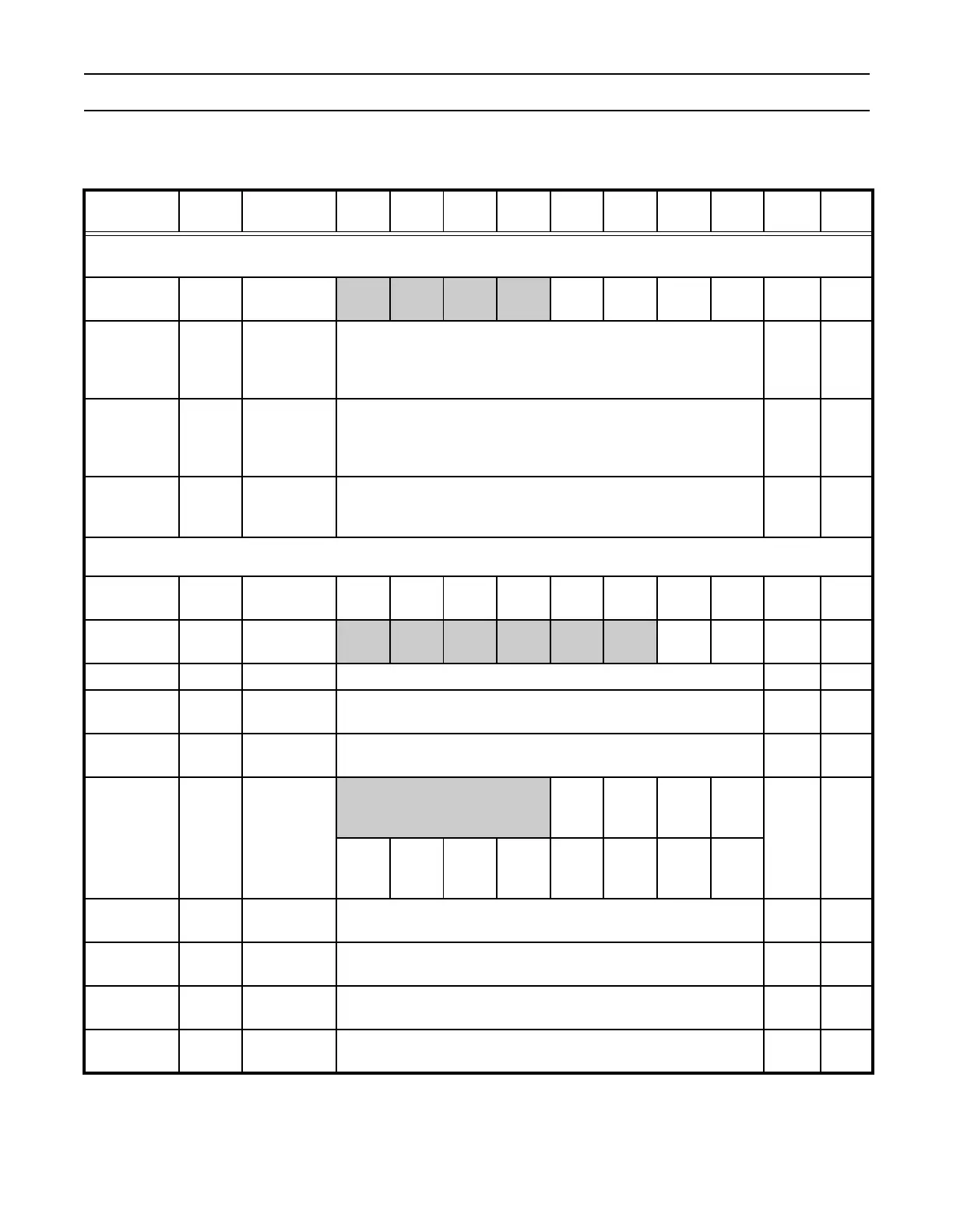

Unused (reserved) bits are marked with "-" and represented as gray fields. Access to them is restricted as already described.

Table 2: LPC2119/2129/2194/2292/2294 Registers

Address

Offset

Name Description MSB LSB Access

Reset

Value

WD

0xE0000000

WD

MOD

Watchdog

mode register

- - - -

WD

INT

WD

TOF

WDRE

SET

WDEN R/W 0

0xE0000004 WDTC

Watchdog

timer

constant

register

32 bit data R/W 0xFF

0xE0000008

WD

FEED

Watchdog

feed

sequence

register

8 bit data (0xAA fallowed by 0x55) WO NA

0xE000000C WDTV

Watchdog

timer value

register

32 bit data RO 0xFF

TIMER0

0xE0004000 T0IR

T0 Interrupt

Register

CR3

Int.

CR2

Int.

CR1

Int.

CR0

Int.

MR3

Int.

MR2

Int.

MR1

Int.

MR0

Int.

R/W 0

0xE0004004 T0TCR

T0 Control

Register

- - - - - -

CTR

Reset

CTR

Enable

R/W 0

0xE0004008 T0TC T0 Counter 32 bit data RW 0

0xE000400C T0PR

T0 Prescale

Register

32 bit data R/W 0

0xE0004010 T0PC

T0 Prescale

Counter

32 bit data R/W 0

0xE0004014 T0MCR

T0 Match

Control

Register

4 reserved (-) bits

Stop

on

MR3

Reset

on

MR3

Int. on

MR3

Stop

on

MR2

R/W 0

Reset

on

MR2

Int. on

MR2

Stop

on

MR1

Reset

on

MR1

Int. on

MR1

Stop

on

MR0

Reset

on

MR0

Int. on

MR0

0xE0004018 T0MR0

T0 Match

Register 0

32 bit data R/W 0

0xE000401C T0MR1

T0 Match

Register 1

32 bit data R/W 0

0xE0004020 T0MR2

T0 Match

Register 2

32 bit data R/W 0

0xE0004024 T0MR3

T0 Match

Register 3

32 bit data R/W 0

Loading...

Loading...