External Memory Controller (EMC) 58 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

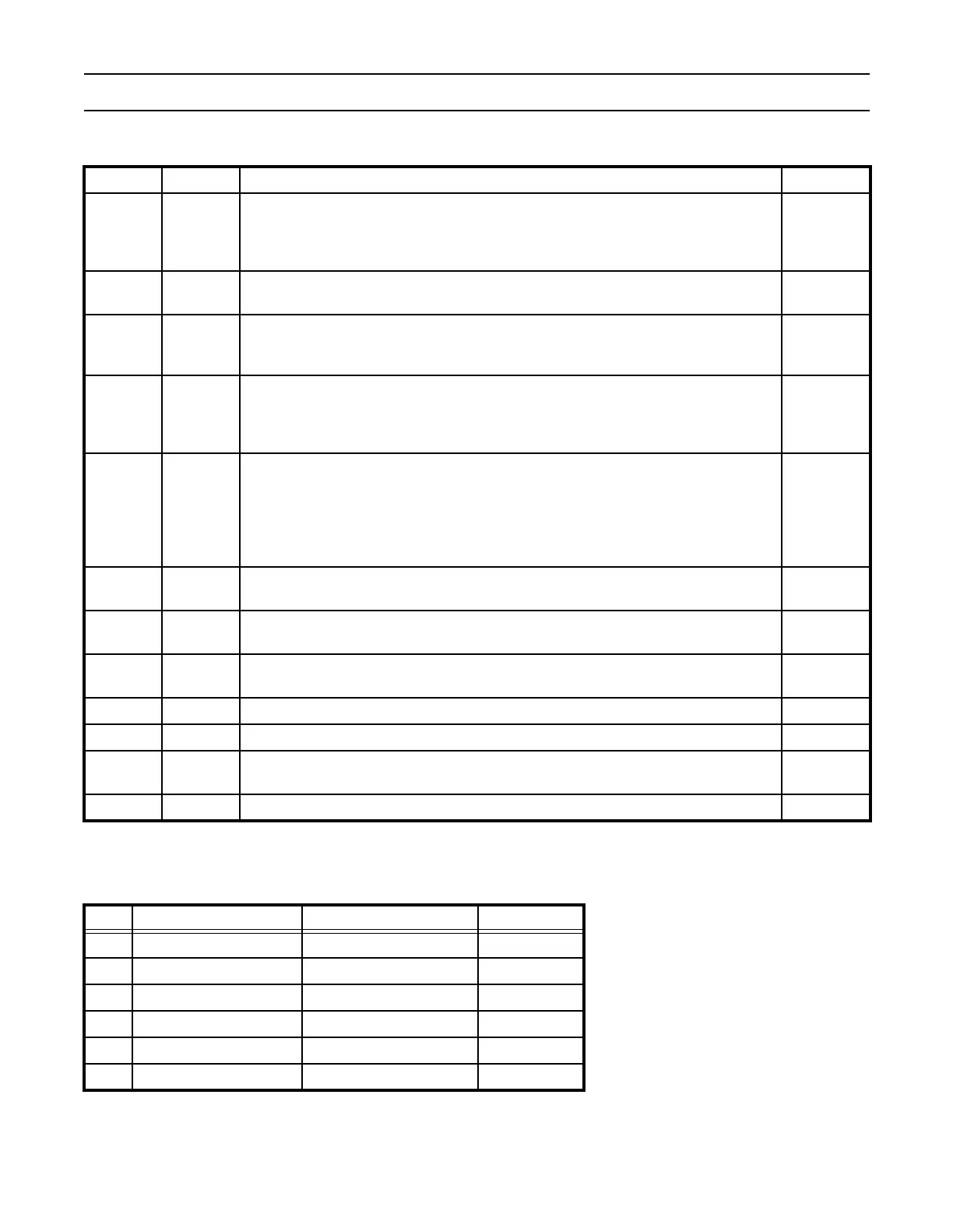

Bank Configuration Registers 0 - 3 (BCFG0-3 - 0xFFE00000-0C).

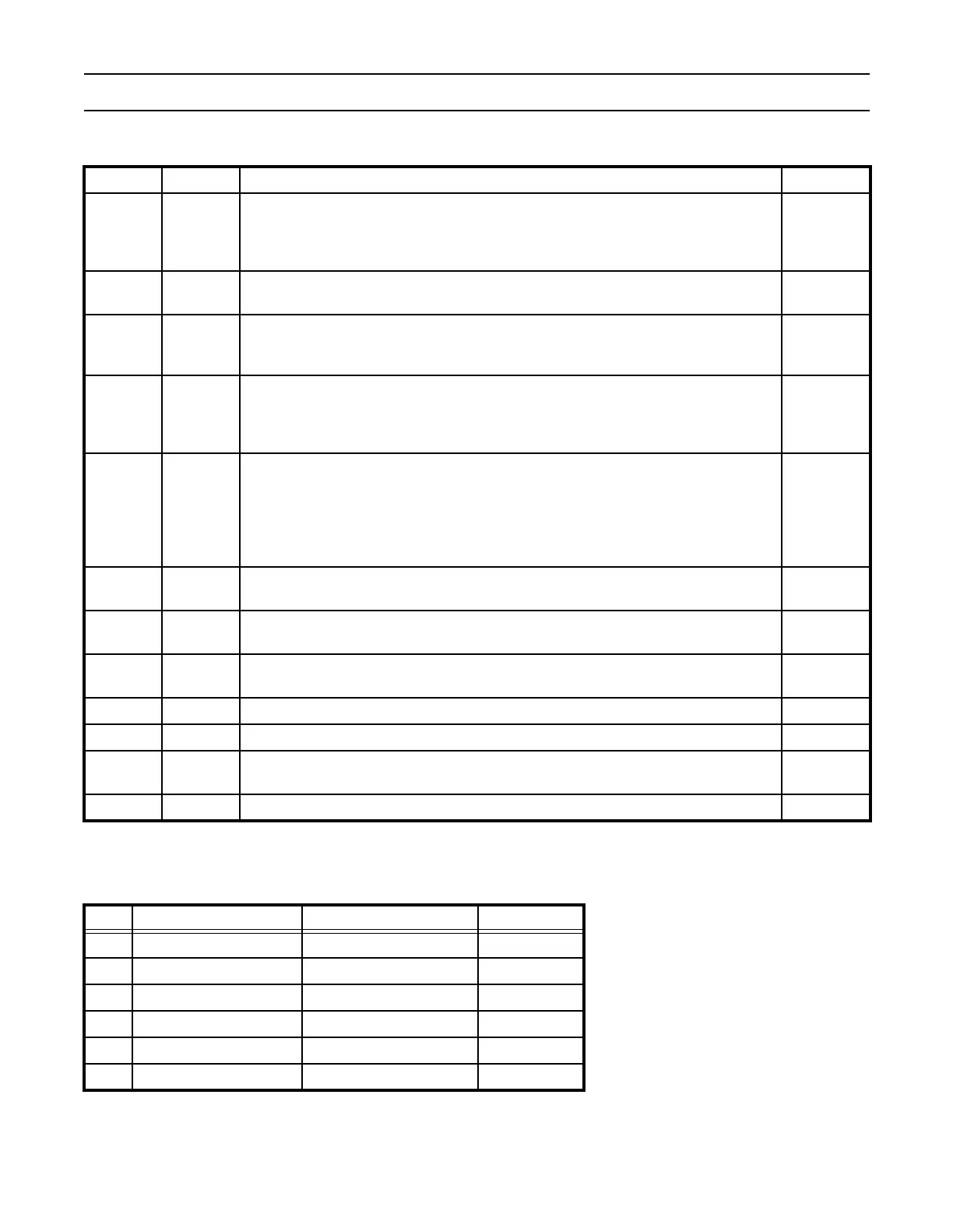

The table below shows the state of BCFG0[29:28] after the Boot Loader has run. The hardware reset state of these bits is 10.

BCFG0-3 Name Function Reset Value

3:0 IDCY

This field controls the minimum number of “idle” CCLK cycles that the EMC maintains

between read and write accesses in this bank, and between an access in another bank

and an access in this bank, to avoid bus contention between devices. The number of

idle CCLK cycles between such accesses is the value in this field plus 1.

1111

4 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

9:5 WST1

This field controls the length of read accesses, except for subsequent reads from a

burst ROM. The length of such read accesses, in CCLK cycles, is the value in this field

plus 3.

11111

10 RBLE

This bit should be 0 for banks composed of byte-wide or non-byte-partitioned devices,

so that the EMC drives the BLS3:0 lines High during read accesses. This bit should be

1 for banks composed of 16-bit and 32-bit wide devices that include byte select inputs,

so that the EMC drives the BLS3:0 lines Low during read accesses.

0

15:11 WST2

For SRAM banks, this field controls the length of write accesses, which consist of:

• one CCLK cycle of address setup with CS, BLS, and WE high,

• (this value plus 1) CCLK cycles with address valid and CS, BLS, and WE low, and

• one CCLK cycle with address valid, CS low, BLS and WE high.

For burst ROM banks, this field controls the length of subsequent accesses, which are

(this value plus 1) CCLK cycles long.

11111

16:23 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

24 BUSERR

The only known case in which this bit is set is if the EMC detects an AMBA request for

more than 32 bits of data. The ARM7TDMI-S will not make such a request.

0

25 WPERR

This bit is set if software attempts to write to a bank that has the WP bit 1. Write a 1 to

this bit to clear it.

0

26 WP A 1 in this bit write-protects the bank. 0

27 BM A 1 in this bit identifies a burst-ROM bank. 0

29:28 MW

This field controls the width of the data bus for this bank:

00=8 bit, 01=16 bit, 10=32 bit, 11=reserved

see Table 9

31:30 AT Always write 00 to this field. 00

Table 8: Bank Configuration Registers 0-3 (BCFG0-3 - 0xFFE00000-0C)

Bank BOOT[1:0] during Reset BCFG[29:28] Reset value Memory Width

0 LL 00 8 bits

0LH 01 16 bits

0HL 10 32 bits

1XX 10 32 bits

2XX 01 16 bits

3XX 00 8 bits

Table 9: Default memory widths at Reset

Loading...

Loading...