CAN Controllers and Acceptance Filter 197 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2292/2294ARM-based Microcontroller

Bus Timing Register (CANBTR - 0xE00x x014)

This register controls how various CAN timings are derived from the VPB clock. It can be read at any time, but can only be written

if the RM bit in CANmod is 1. See Table 124 for details on specific CAN channel register address.

Error Warning Limit Register (CANEWL - 0xE00x x018)

This register sets a limit on Tx or Rx errors at which an interrupt can occur. It can be read at any time, but can only be written if

the RM bit in CANmod is 1. See Table 124 for details on specific CAN channel register address.

Status Register (CANSR - 0xE00x x01C)

This register contains three status bytes, in which the bits not related to tranmission are identical to the corresponding bits in the

Global Status Register, while those relating to transmission reflect the status of each of the 3 Tx Buffers. See Table 124 for details

on specific CAN channel register address.

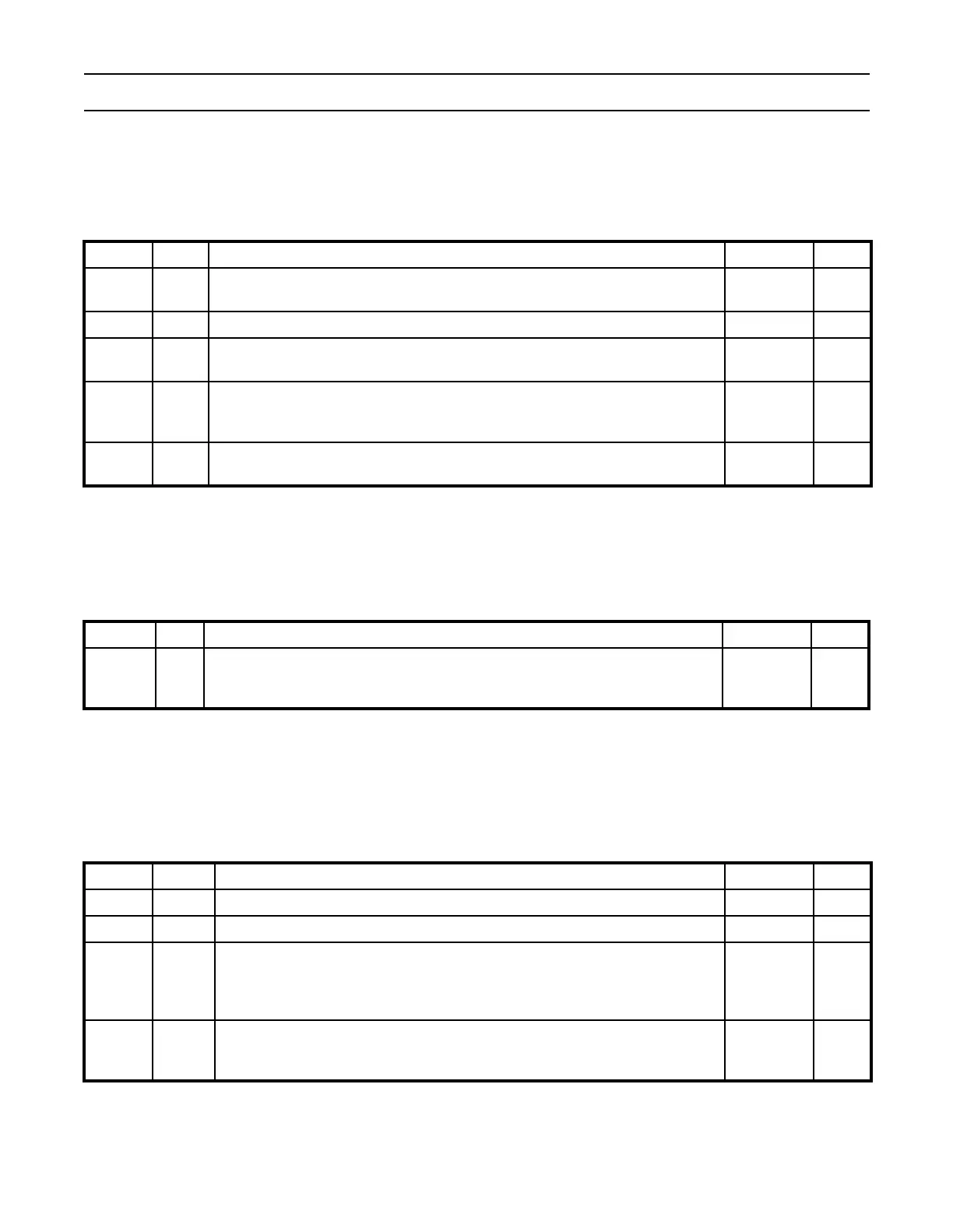

Table 130: CAN Bus Timing Register (CANBTR - 0xE00x x014)

CANBTR Name Function Reset Value RM Set

0:9 BRP

Baud Rate Prescaler. The VPB clock is divided by (this value plus one) to produce

the CAN clock.

0X

15:14 SJW The Synchronization Jump Width is (this value plus one) CAN clocks. 0 X

19:16 TSEG1

The delay from the nominal Sync point to the sample point is (this value plus one)

CAN clocks.

1100 X

22:20 TSEG2

The delay from the sample point to the next nominal sync point is (this value plus

one) CAN clocks. The nominal CAN bit time is (this value plus the value in TSEG1

plus 3) CAN clocks.

001 X

23 SAM

1: the bus is sampled 3 times (recommended for low to medium speed buses)

0: the bus is sampled once (recommended for high speed buses)

0X

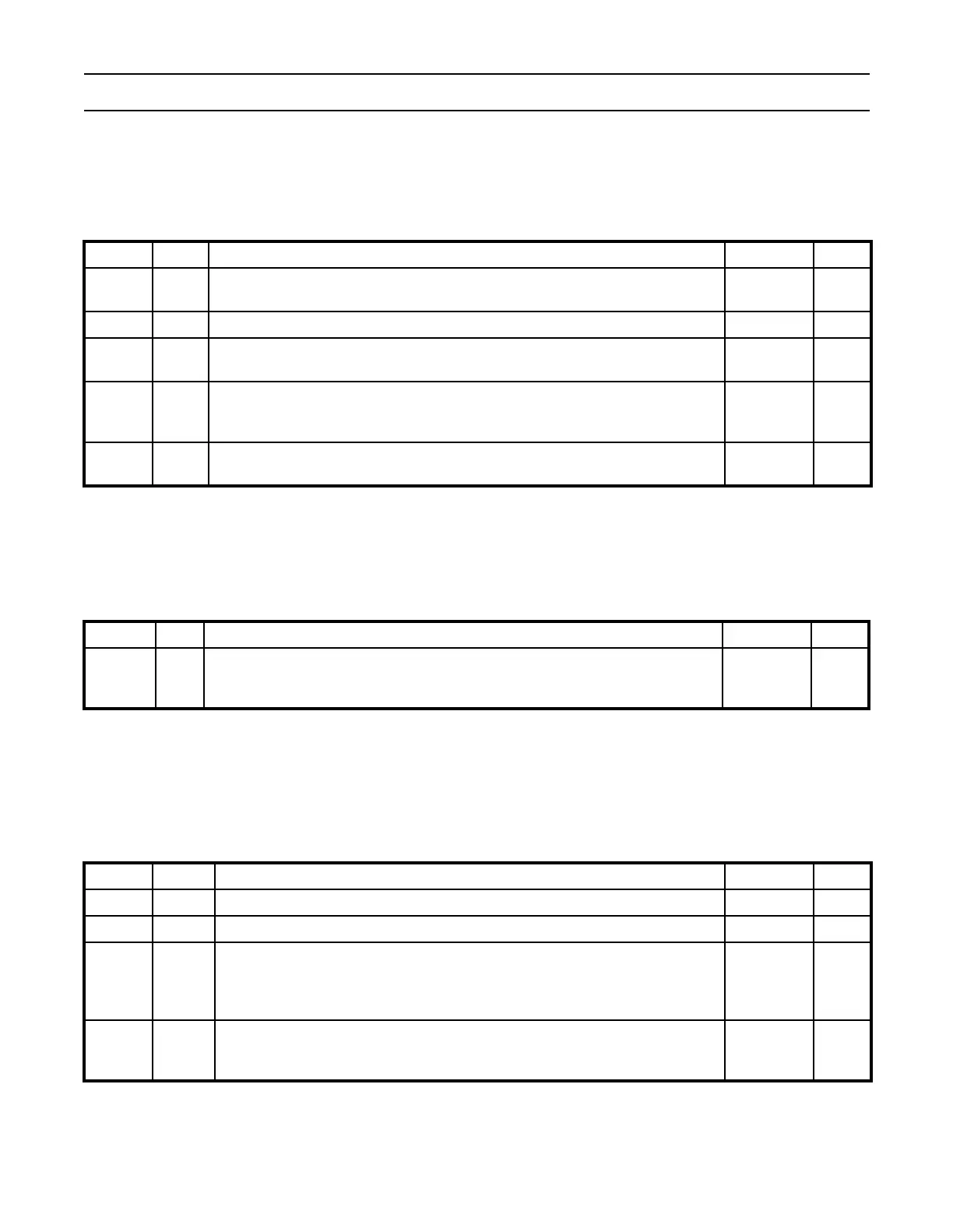

Table 131: CAN Error Warning Limit Register (CANEWL - 0xE00x x018)

CANEWL Name Function Reset Value RM Set

7:0 EWL

During CAN operation, this value is compared to both the Tx and Rx Error Counters.

If either of these counter matches this value, the Error Status (ES) bit in CANSR is

set.

96

10

=0x60 X

Table 132: CAN Status Register (CANSR - 0xE00x x01C)

CANSR Name Function Reset Value RM Set

0, 8, 16 RBS These bits are identical to the RSB bit in the GSR. 0 0

1, 9, 17 DOS These bits are identical to the DOS bit in the GSR. 0 0

2, 10, 18

TBS1,

TBS2,

TBS3

1: software may write a message into the CANTFI, CANTID, CANTDA, and

CANTDB registers for this Tx Buffer.

0: software should not write to any of the CANTFI, CANTID, CANTDA, and

CANTDB registers for this Tx Buffer.

1X

3, 11, 19

TCS1,

TCS2,

TCS3

1: The previously requested transmission for this Tx Buffer has been successfully

completed.

0: The previously requested transmission for this Tx Buffer is not complete.

10

Loading...

Loading...