UART1 157 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

The UART1 THRE interrupt (U1IIR3:1=001) is a third level interrupt and is activated when the UART1 THR FIFO is empty

provided certain initialization conditions have been met. These initialization conditions are intended to give the UART1 THR FIFO

a chance to fill up with data to eliminate many THRE interrupts from occurring at system start-up. The initialization conditions

implement a one character delay minus the stop bit whenever THRE=1 and there have not been at least two characters in the

U1THR at one time since the last THRE=1 event. This delay is provided to give the CPU time to write data to U1THR without a

THRE interrupt to decode and service. A THRE interrupt is set immediately if the UART1 THR FIFO has held two or more

characters at one time and currently, the U1THR is empty. The THRE interrupt is reset when a U1THR write occurs or a read of

the U1IIR occurs and the THRE is the highest interrupt (U1IIR3:1=001).

The modem interrupt (U1IIR3:1=000) is the lowest priority interrupt and is activated whenever there is any state change on

modem inputs pins, DCD, DSR or CTS. In addition, a low to high transition on modem input RI will generate a modem interrupt.

The source of the modem interrupt can be determined by examining U1MSR3:0. A U1MSR read will clear the modem interrupt.

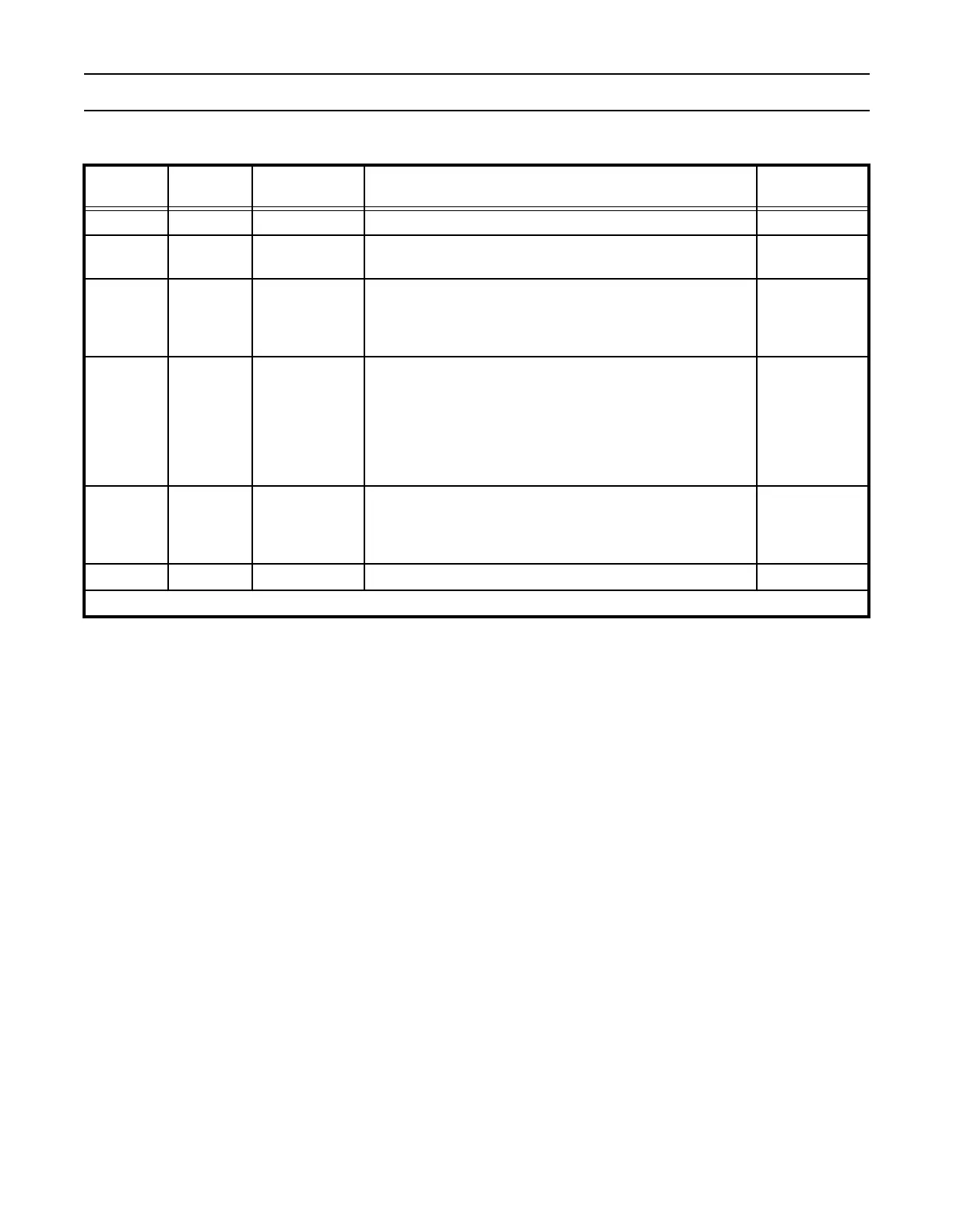

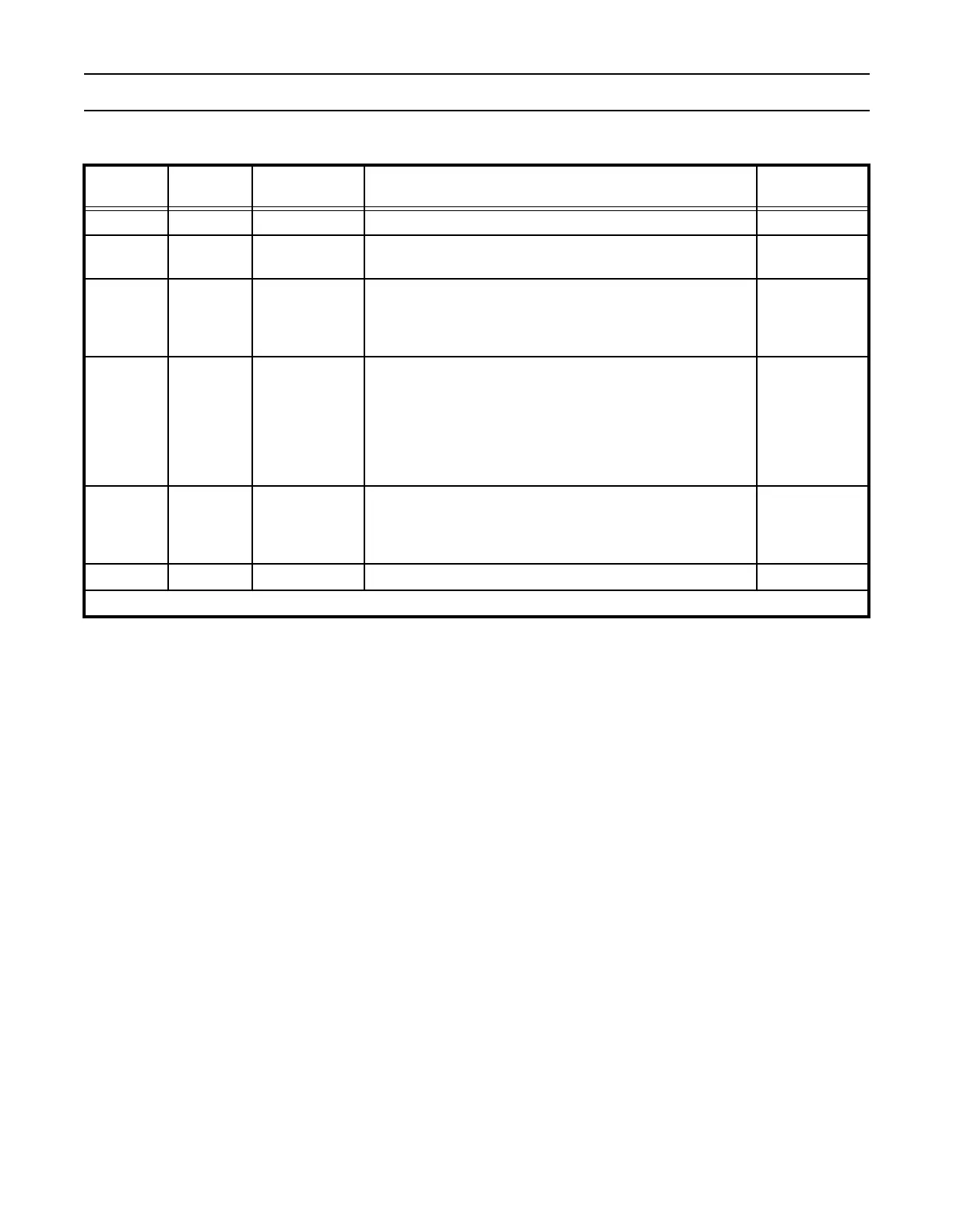

Table 94: UART1 Interrupt Handling

U1IIR[3:0] Priority

Interrupt

Type

Interrupt

Source

Interrupt

Reset

0001 - none none -

0110 Highest

Rx Line Status /

Error

OE or PE or FE or BI U1LSR Read

0100 Second

Rx Data

Available

Rx data available or trigger level reached in FIFO mode

(FCR0=1)

U1RBR Read or

UART1 FIFO

drops below

trigger level

1100 Second

Character Time-

out Indication

Minimum of one character in the Rx FIFO and no character

input or removed during a time period depending on how many

characters are in FIFO and what the trigger level is set at (3.5

to 4.5 character times).

The exact time will be:

[(word length) X 7 - 2] X 8 + {(trigger level - number of

characters) X 8 + 1] RCLKs

U1RBR Read

0010 Third THRE THRE

U1IIR Read (if

source of

interrupt) or

THR write

0000 Fourth Modem Status CTS or DSR or RI or DCD MSR Read

note: values “0011”. “0101”, “0111”, “1000”, “1001”, “1010”, “1011”,”1101”,”1110”,”1111” are reserved.

Loading...

Loading...