Vectored Interrupt Controller (VIC) 97 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

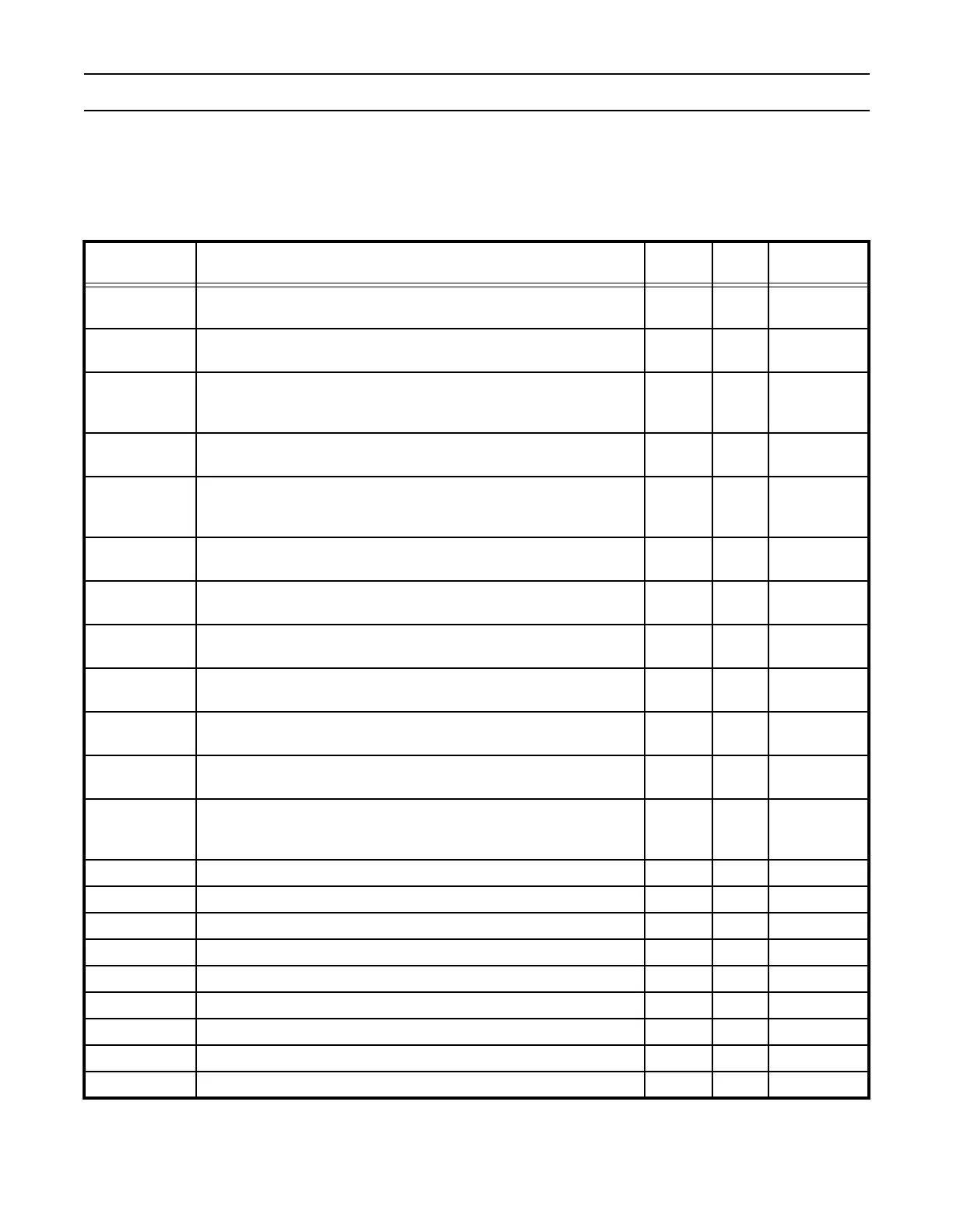

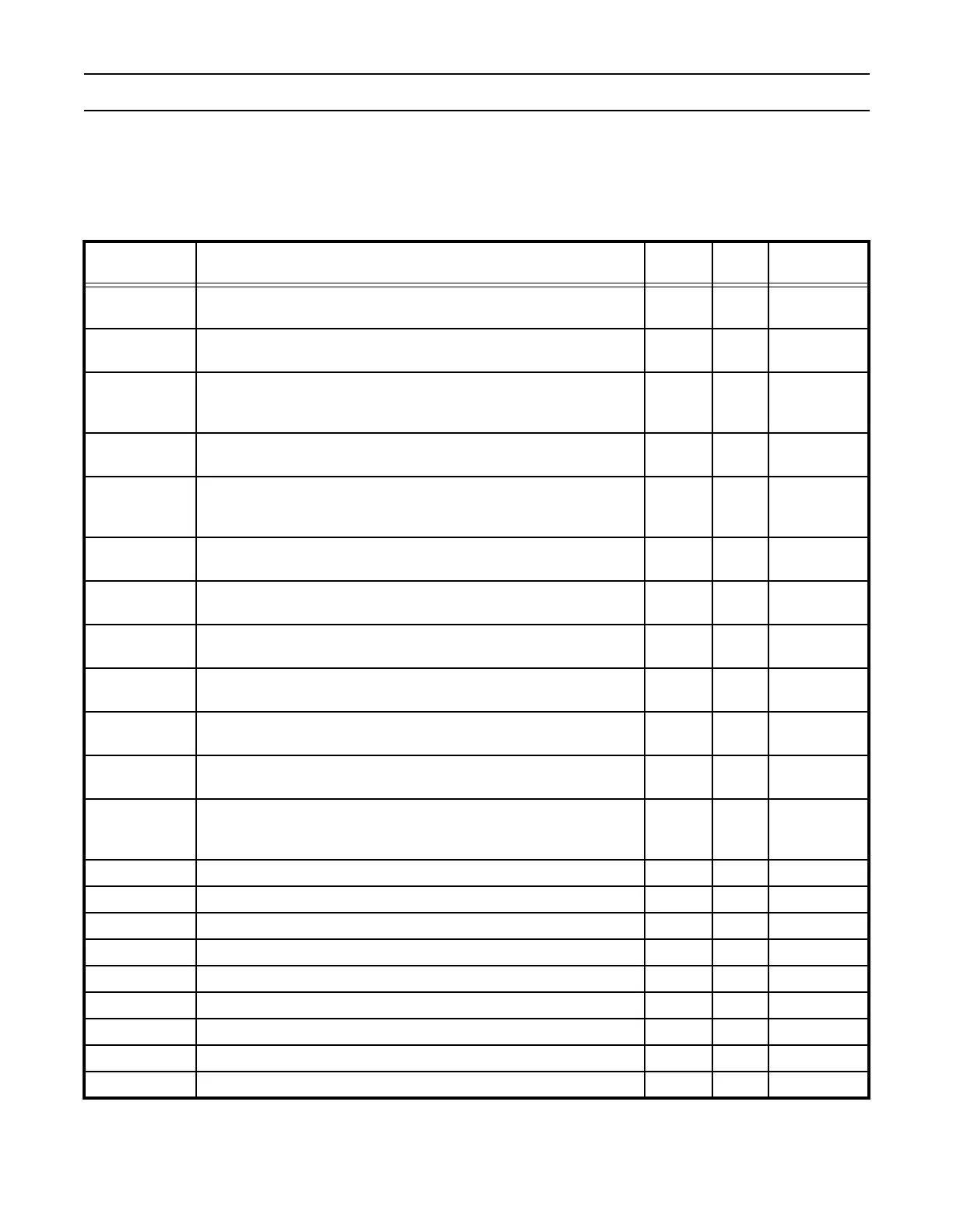

REGISTER DESCRIPTION

The VIC implements the registers shown in Table 40. More detailed descriptions follow.

Table 40: VIC Register Map

Name Description Access

Reset

Value*

Address

VICIRQStatus

IRQ Status Register. This register reads out the state of those interrupt

requests that are enabled and classified as IRQ.

RO 0 0xFFFF F000

VICFIQStatus

FIQ Status Requests. This register reads out the state of those interrupt

requests that are enabled and classified as FIQ.

RO 0 0xFFFF F004

VICRawIntr

Raw Interrupt Status Register. This register reads out the state of the 32

interrupt requests / software interrupts, regardless of enabling or

classification.

RO 0 0xFFFF F008

VICIntSelect

Interrupt Select Register. This register classifies each of the 32 interrupt

requests as contributing to FIQ or IRQ.

R/W 0 0xFFFF F00C

VICIntEnable

Interrupt Enable Register. This register controls which of the 32 interrupt

requests and software interrupts are enabled to contribute to FIQ or

IRQ.

R/W 0 0xFFFF F010

VICIntEnClr

Interrupt Enable Clear Register. This register allows software to clear

one or more bits in the Interrupt Enable register.

W 0 0xFFFF F014

VICSoftInt

Software Interrupt Register. The contents of this register are ORed with

the 32 interrupt requests from various peripheral functions.

R/W 0 0xFFFF F018

VICSoftIntClear

Software Interrupt Clear Register. This register allows software to clear

one or more bits in the Software Interrupt register.

W 0 0xFFFF F01C

VICProtection

Protection enable register. This register allows limiting access to the VIC

registers by software running in privileged mode.

R/W 0 0xFFFF F020

VICVectAddr

Vector Address Register. When an IRQ interrupt occurs, the IRQ service

routine can read this register and jump to the value read.

R/W 0 0xFFFF F030

VICDefVectAddr

Default Vector Address Register. This register holds the address of the

Interrupt Service routine (ISR) for non-vectored IRQs.

R/W 0 0xFFFF F034

VICVectAddr0

Vector address 0 register. Vector Address Registers 0-15 hold the

addresses of the Interrupt Service routines (ISRs) for the 16 vectored

IRQ slots.

R/W 0 0xFFFF F100

VICVectAddr1 Vector address 1 register R/W 0 0xFFFF F104

VICVectAddr2 Vector address 2 register R/W 0 0xFFFF F108

VICVectAddr3 Vector address 3 register R/W 0 0xFFFF F10C

VICVectAddr4 Vector address 4 register R/W 0 0xFFFF F110

VICVectAddr5 Vector address 5 register R/W 0 0xFFFF F114

VICVectAddr6 Vector address 6 register R/W 0 0xFFFF F118

VICVectAddr7 Vector address 7 register R/W 0 0xFFFF F11C

VICVectAddr8 Vector address 8 register R/W 0 0xFFFF F120

VICVectAddr9 Vector address 9 register R/W 0 0xFFFF F124

Loading...

Loading...