CAN Controllers and Acceptance Filter 195 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2292/2294ARM-based Microcontroller

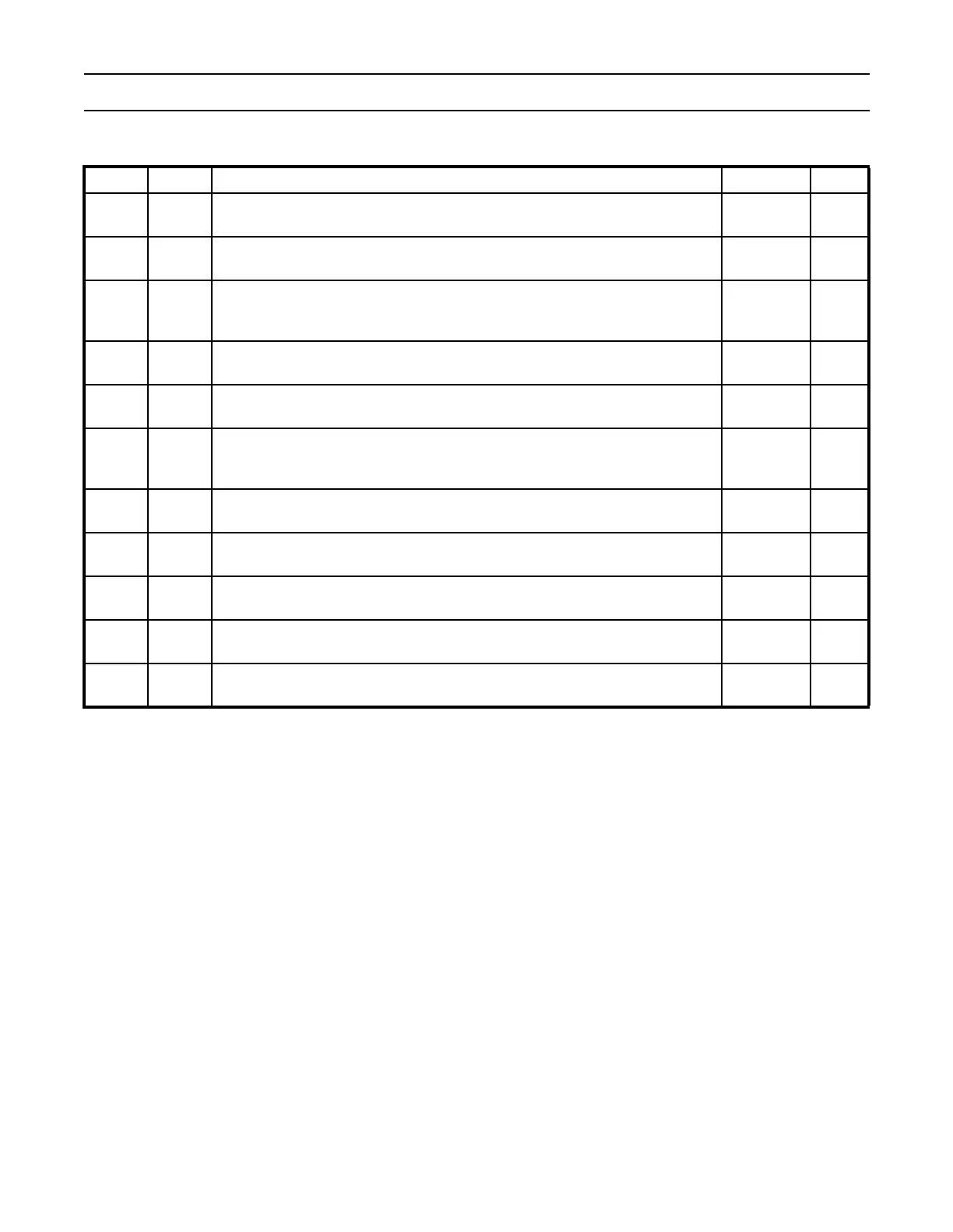

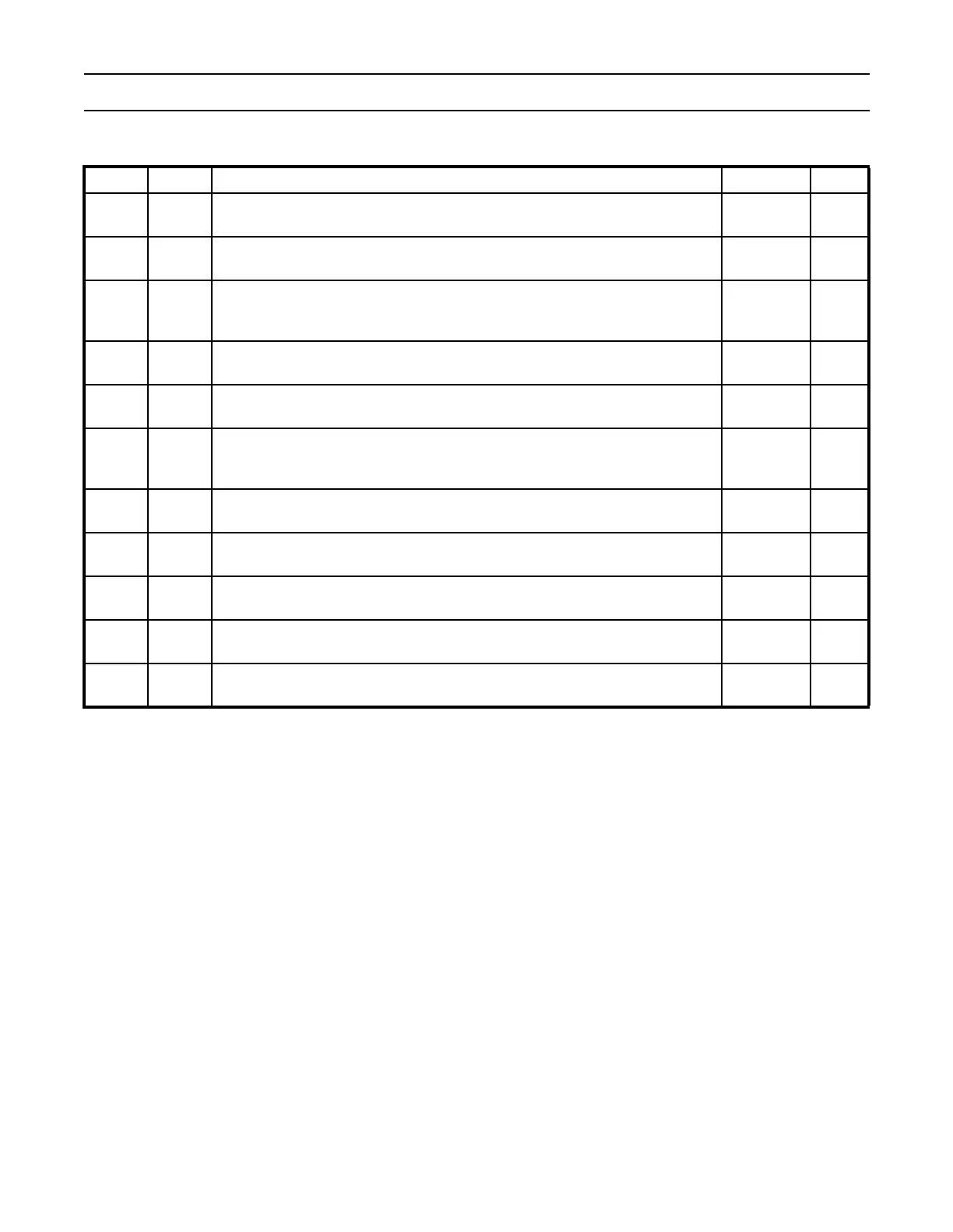

Table 128: CAN Interrupt and Capture Register (CANICR - 0xE00x x00C)

CANICR Name Function Reset Value RM Set

0RI

1: Receive Interrupt -- this bit is set whenever the RBS bit in CANSR and the RIE

bit in CANIER are both 1, indicating that a received message is available.=.

00

1TI1

1: Transmit Interrupt 1 -- this bit is set when the TBS1 bit in CANSR goes from 0

to 1, indicating that Transmit buffer 1 is available, and the TIE1 bit in CANIER is 1.

00

2EI

1: Error Warning Interrupt -- this bit is set on every change (set or clear) of the Error

Status or Bus Status bit in CANSR, if the EIE bit in CAN is 1 at the time of the

change.

0X

3DOI

1: Data Overrun Interrupt -- this bit is set when the DOS bit in CANSR goes from

0 to 1, if the DOIE bit in CANIE is 1.

00

4WUI

1: Wake-Up Interrupt: this bit is set if the CAN controller is sleeping and bus activity

is detected, if the WUIE bit in CANIE is 1.

00

5 EPI

1: Error Passive Interrupt -- this bit is set if the EPIE bit in CANIE is 1, and the CAN

controller switches between Error Passive and Error Active mode in either

direction.

00

6ALI

1: Arbitration Lost Interrupt -- this bit is set if the ALIE bit in CANIE is 1, and the

CAN controller loses arbitration while attempting to transmit.

00

7 BEI

1: Bus Error Interrupt -- this bit is set if the BEIE bit in CANIE is 1, and the CAN

controller detects an error on the bus.

0X

8IDI

1: ID Ready Interrupt -- this bit is set if the IDIE bit in CANIE is 1, and a CAN

Identifier has been received.

00

9TI2

1: Transmit Interrupt 2 -- this bit is set when the TBS2 bit in CANSR goes from 0

to 1, indicating that Transmit buffer 2 is available, and the TIE2 bit in CANIER is 1.

00

10 TI3

1: Transmit Interrupt 1 -- this bit is set when the TBS3 bit in CANSR goes from 0

to 1, indicating that Transmit buffer 3 is available, and the TIE3 bit in CANIER is 1.

00

Loading...

Loading...