Real Time Clock 246 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

MISCELLANEOUS REGISTER GROUP

Table 177 summarizes the registers located from 0 to 7 of A[6:2]. More detailed descriptions follow.

Interrupt Location (ILR - 0xE0024000)

The Interrupt Location Register is a 2-bit register that specifies which blocks are generating an interrupt (see Table 178). Writing

a one to the appropriate bit clears the corresponding interrupt. Writing a zero has no effect. This allows the programmer to read

this register and write back the same value to clear only the interrupt that is detected by the read.

Clock Tick Counter (CTC - 0xE0024004)

The Clock Tick Counter is read only. It can be reset to zero through the Clock Control Register (CCR). The CTC consists of the

bits of the clock divider counter.

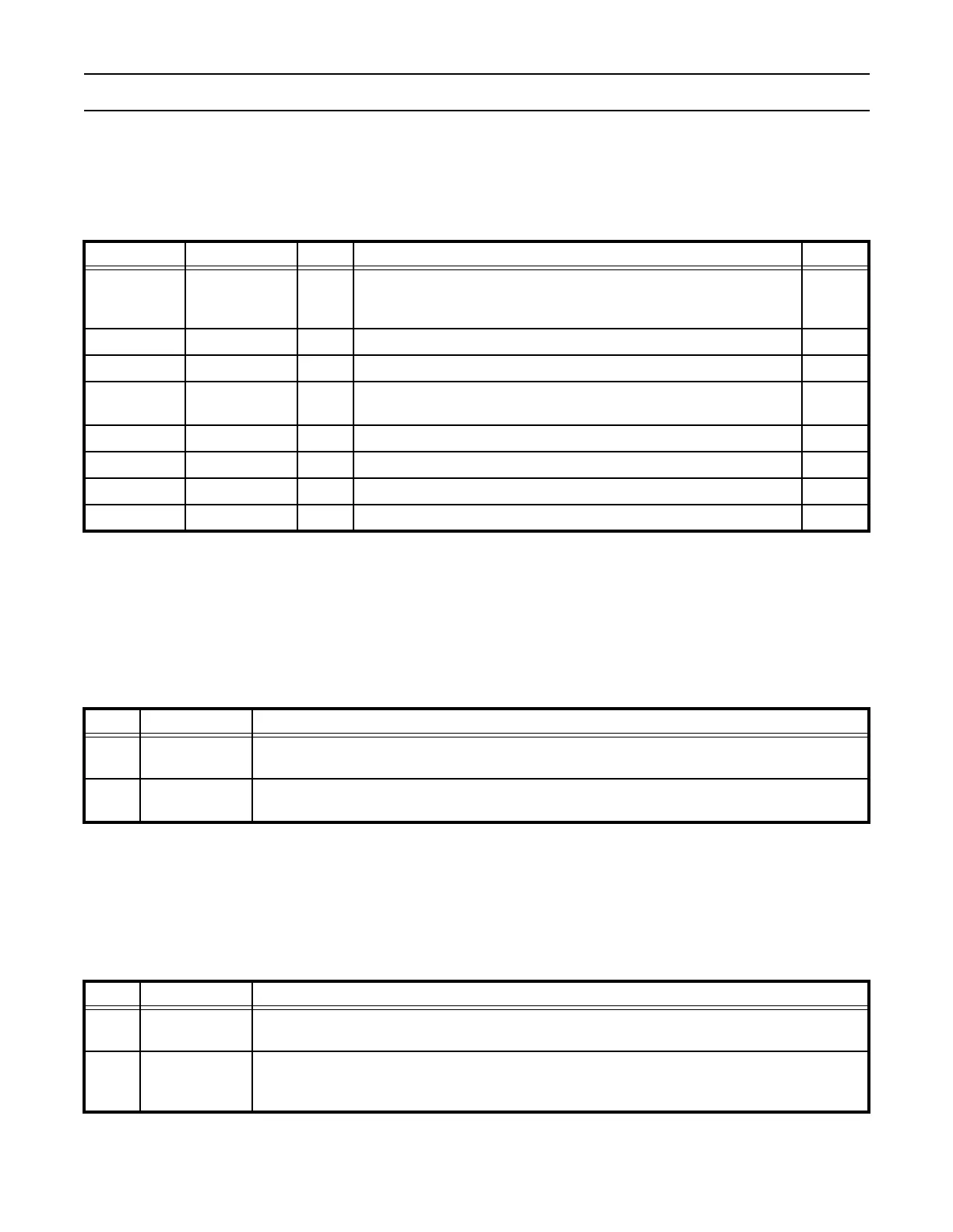

Table 177: Miscellaneous Registers

Address Name Size Description Access

0xE0024000 ILR 2

Interrupt Location. Reading this location indicates the source of an

interrupt. Writing a one to the appropriate bit at this location clears the

associated interrupt.

RW

0xE0024004 CTC 15 Clock Tick Counter. Value from the clock divider. RO

0xE0024008 CCR 4 Clock Control Register. Controls the function of the clock divider. RW

0xE002400C CIIR 8

Counter Increment Interrupt. Selects which counters will generate an

interrupt when they are incremented.

RW

0xE0024010 AMR 8 Alarm Mask Register. Controls which of the alarm registers are masked. RW

0xE0024014 CTIME0 32 Consolidated Time Register 0 RO

0xE0024018 CTIME1 32 Consolidated Time Register 1 RO

0xE002401C CTIME2 32 Consolidated Time Register 2 RO

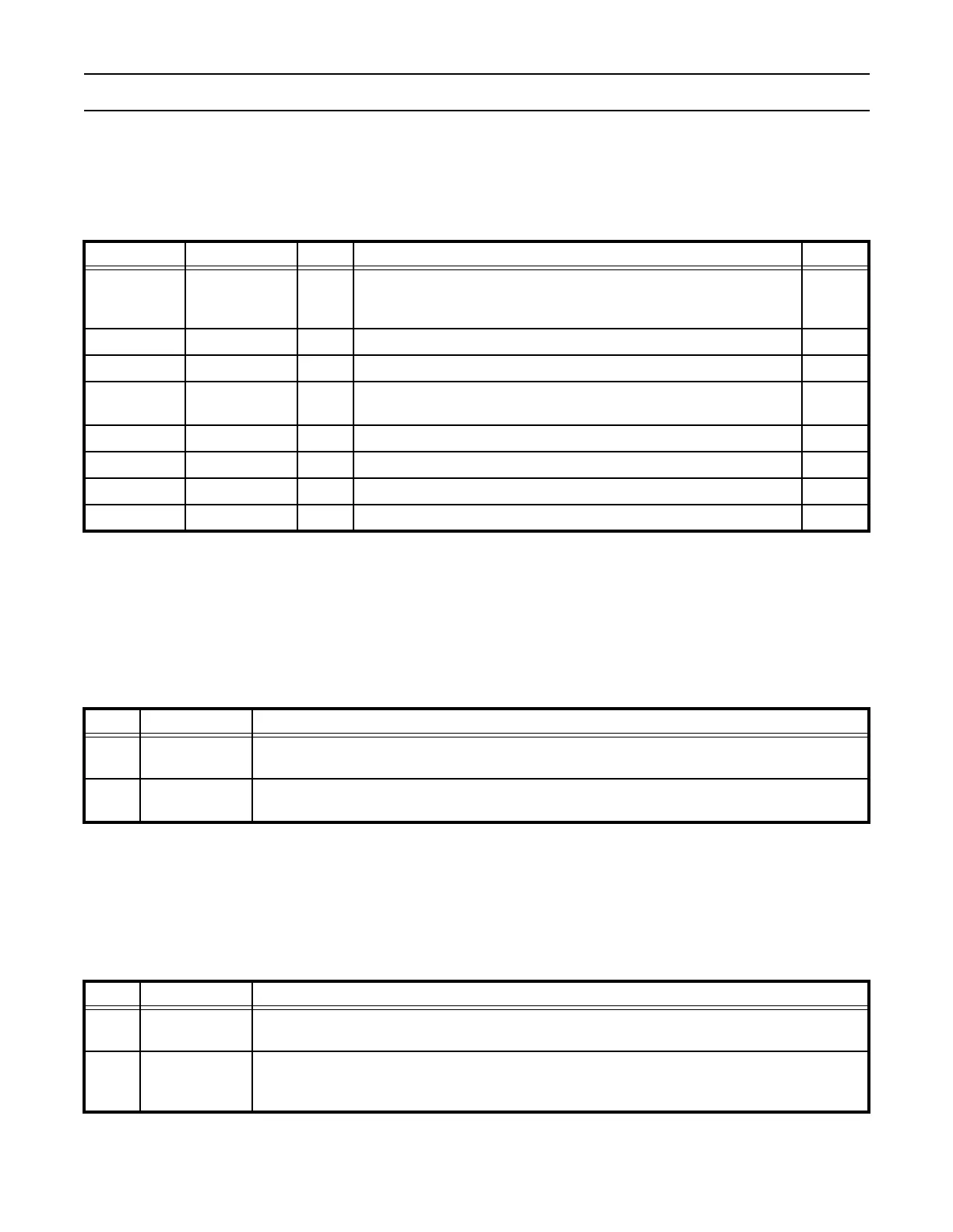

Table 178: Interrupt Location Register Bits (ILR - 0xE0024000)

ILR Function Description

0 RTCCIF

When one, the Counter Increment Interrupt block generated an interrupt. Writing a one to this bit

location clears the counter increment interrupt.

1RTCALF

When one, the alarm registers generated an interrupt. Writing a one to this bit location clears the

alarm interrupt.

Table 179: Clock Tick Counter Bits (CTC - 0xE0024004)

CTC Function Description

0 Reserved

Reserved, user software should not write ones to reserved bits. The value read from a reserved bit

is not defined.

15:1

Clock Tick

Counter

Prior to the Seconds counter, the CTC counts 32,768 clocks per second. Due to the RTC Prescaler,

these 32,768 time increments may not all be of the same duration. Refer to the Reference Clock

Divider (Prescaler) description for details.

Loading...

Loading...