I2C Interface 174 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

I

2

C Status Register (I2STAT - 0xE001C004)

This is a read-only register. It contains the status code of the I

2

C interface. The least three bits are always 0. There are 26

possible status codes. When the code is F8H, there is no relevant information available and the SI bit is not set. All other 25 status

codes correspond to defined I

2

C states. When any of these states entered, SI bit will be set. Refer to Table 3 to Table 6 in "80C51

Family Derivatives 8XC552/562 Overview" datasheet available on-line at

http://www.semiconductors.philips.com/acrobat/various/8XC552_562OVERVIEW_2.pdf

for a complete list of status codes.

I

2

C Data Register (I2DAT - 0xE001C008)

This register contains the data to be transmitted or the data just received. The CPU can read and write to this register while it is

not in the process of shifting a byte. This register can be accessed only when SI bit is set. Data in I2DAT remains stable as long

as the SI bit is set. Data in I2DAT is always shifted from right to left: the first bit to be transmitted is the MSB (bit 7), and after a

byte has been received, the first bit of received data is located at the MSB of I2DAT.

I

2

C Slave Address Register (I2ADR - 0xE001C00C)

This register is readable and writable, and is only used when the I

2

C is set to slave mode. In master mode, this register has no

effect. The LSB of I2ADR is the general call bit. When this bit is set, the general call address (00h) is recognized.

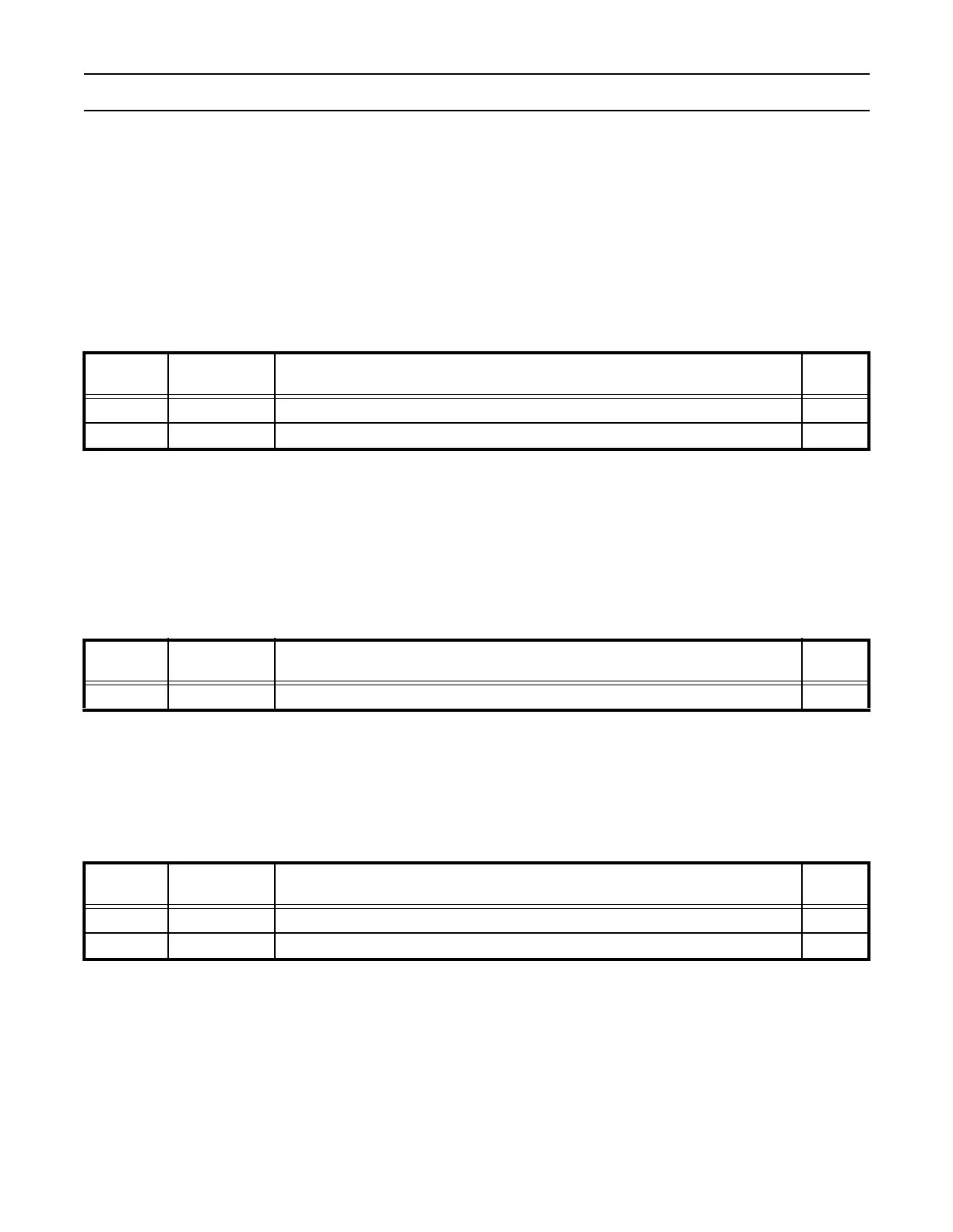

Table 105: I

2

C Status Register (I2STAT - 0xE001C004)

I2STAT Function Description

Reset

Value

2:0 Status These bits are always 0 0

7:3 Status Status bits 1

Table 106: I

2

C Data Register (I2DAT - 0xE001C008)

I2DAT Function Description

Reset

Value

7:0 Data Transmit/Receive data bits 0

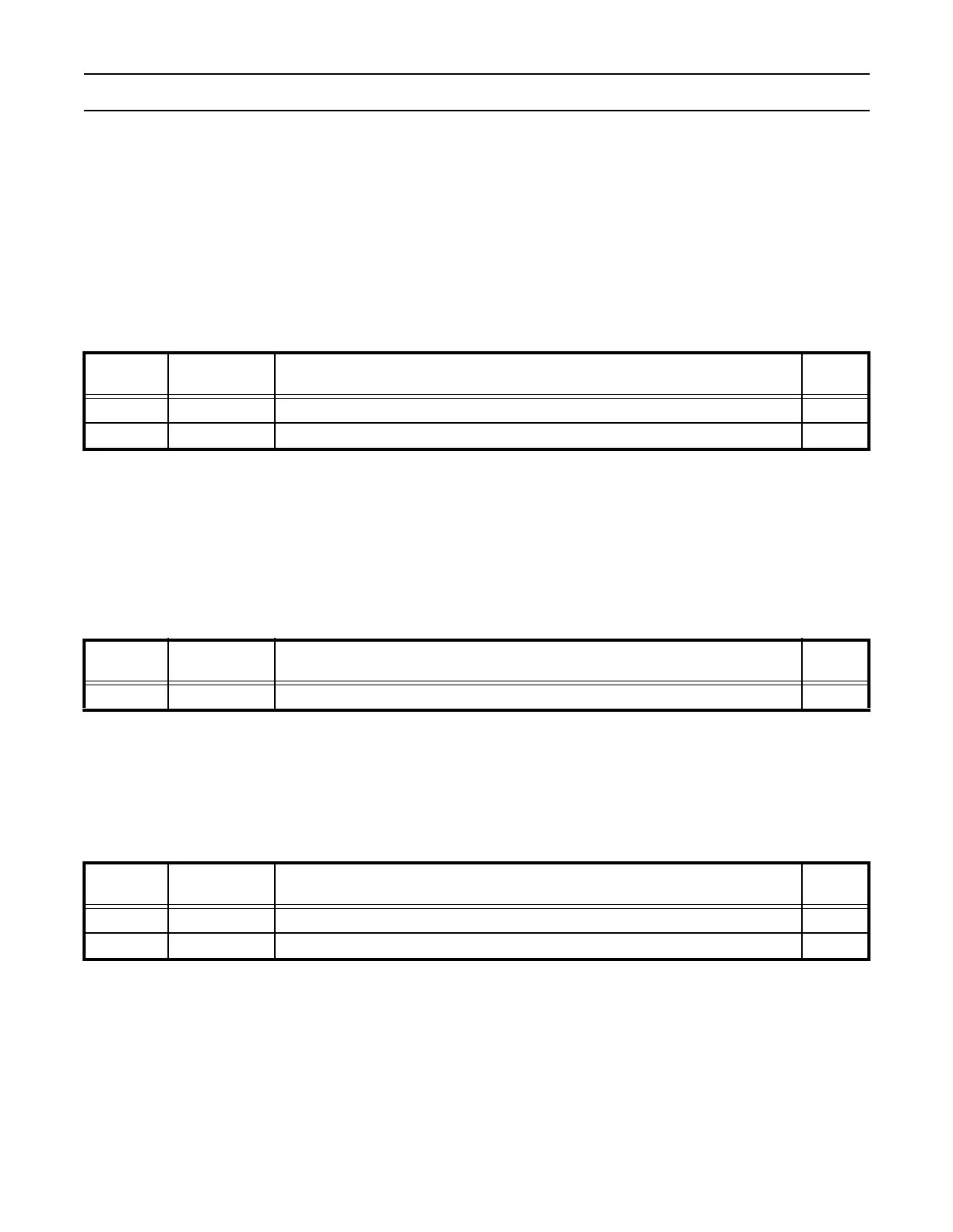

Table 107: I

2

C Slave Address Register (I2ADR - 0xE001C00C)

I2ADR Function Description

Reset

Value

0 GC General Call bit 0

7:1 Address Slave mode address 0

Loading...

Loading...