Pin Configuration 111 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

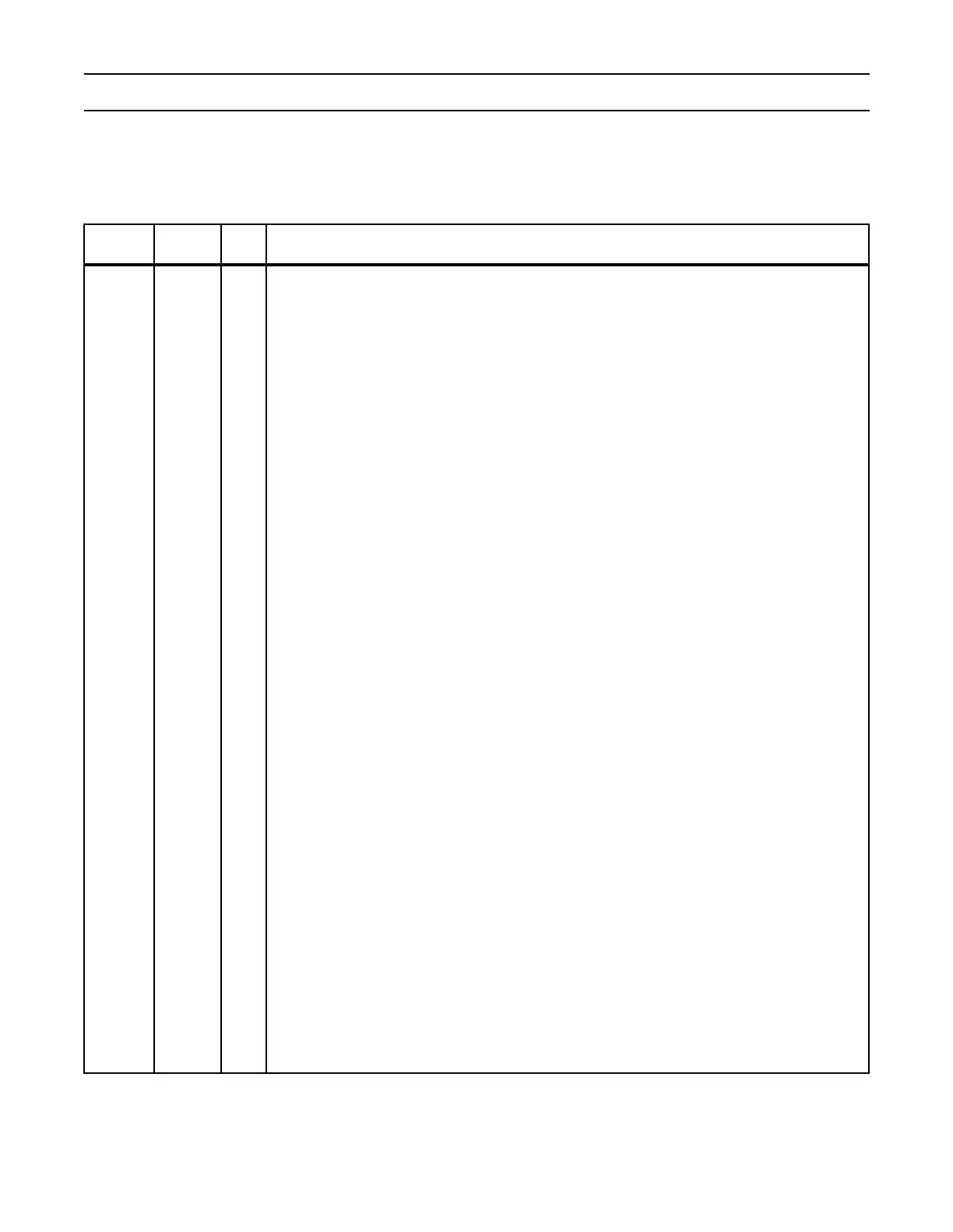

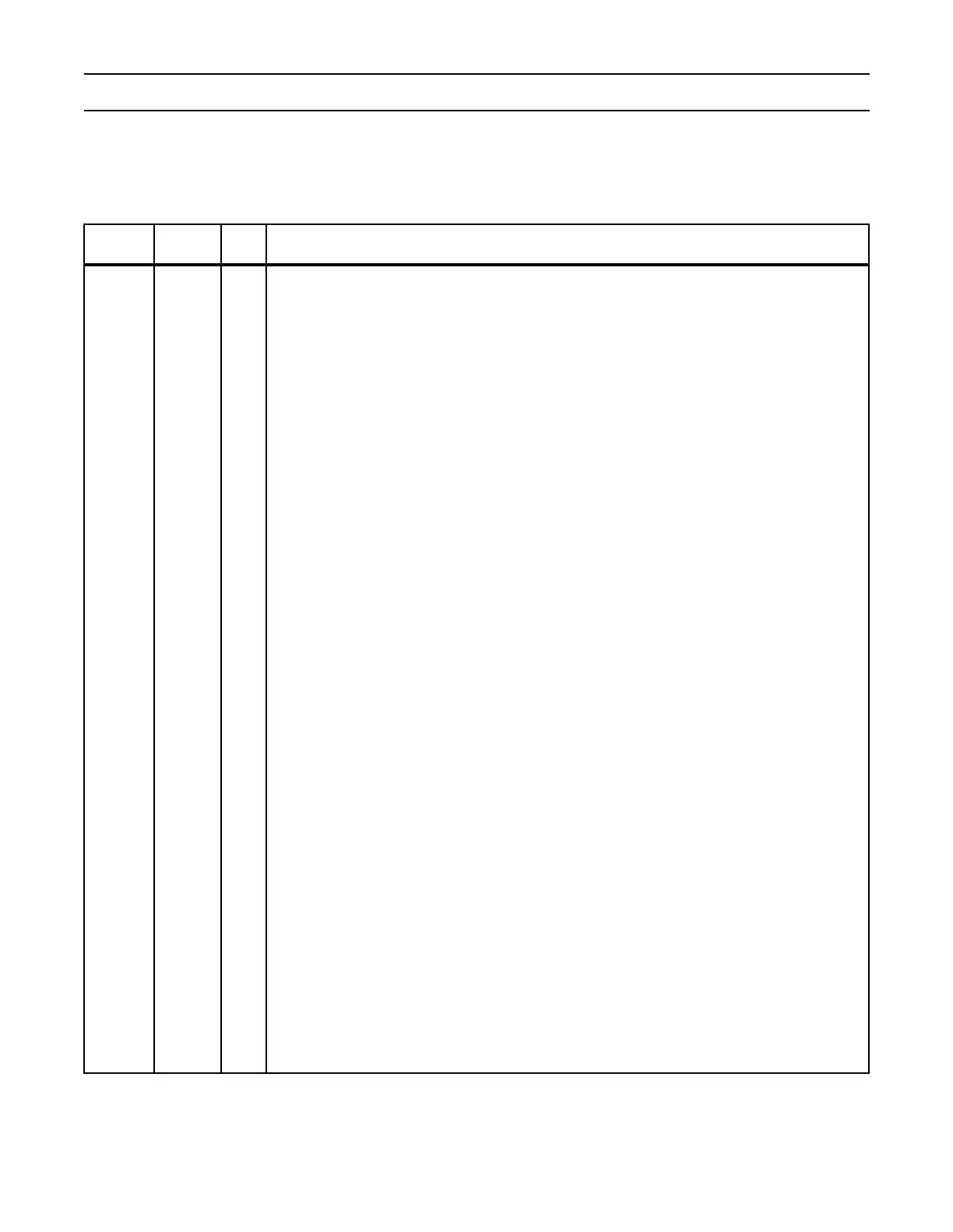

PIN DESCRIPTION FOR LPC2119/2129/2194

Pin description for LPC2119/2129/2194 and a brief of corresponding functions are shown in the following table.

Table 55: Pin description for LPC2119/2129/2194

Pin

Name

LQFP64

Pin #

Type Description

P0.0

to

P0.31

I/O

Port 0: Port 0 is a 32-bit bi-directional I/O port with individual direction controls for each bit. The

operation of port 0 pins depends upon the pin function selected via the Pin Connect Block.

Pins 26 and 31 of port 0 are not available.

Note: All Port 0 pins excluding those that can be used as A/D inputs (P0.27, P0.28, P0.29 and

P0.30) are functionally 5V tolerant. If the A/D converter is not used at all, pins associated with A/

D inputs can be used as 5V tolerant digital IO pins. See "A/D Converter" chapter for A/D input pin

voltage considerations.

19

O

O

P0.0 TxD0 Transmitter output for UART0.

PWM1 Pulse Width Modulator output 1.

21

I

O

I

P0.1 RxD0 Receiver input for UART0.

PWM3 Pulse Width Modulator output 3.

EINT0 External interrupt 0 input.

22

I/O

I

P0.2 SCL I

2

C clock input/output. Open drain output (for I

2

C compliance).

CAP0.0 Capture input for TIMER0, channel 0.

26

I/O

O

P0.3 SDA I

2

C data input/output. Open drain output (for I

2

C compliance).

MAT0.0 Match output for TIMER0, channel 0.

EINT1 External interrupt 1 input.

27

I/O

I

P0.4 SCK0 Serial Clock for SPI0. SPI clock output from master or input to slave.

CAP0.1 Capture input for TIMER0, channel 1.

29

I/O

O

P0.5 MISO0 Master In Slave Out for SPI0. Data input to SPI master or data output

from SPI slave.

MAT0.1 Match output for TIMER0, channel 1.

30

I/O

I

P0.6 MOSI0 Master Out Slave In for SPI0. Data output from SPI master or data

input to SPI slave.

CAP0.2 Capture input for TIMER0, channel 2.

31

I

O

I

P0.7 SSEL0 Slave Select for SPI0. Selects the SPI interface as a slave.

PWM2 Pulse Width Modulator output 2.

EINT2 External interrupt 2 input.

33

O

O

P0.8 TxD1 Transmitter output for UART1.

PWM4 Pulse Width Modulator output 4.

34

I

O

I

P0.9 RxD1 Receiver input for UART1.

PWM6 Pulse Width Modulator output 6.

EINT3 External interrupt 3 input.

Loading...

Loading...