Embedded Trace Macrocell 292 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

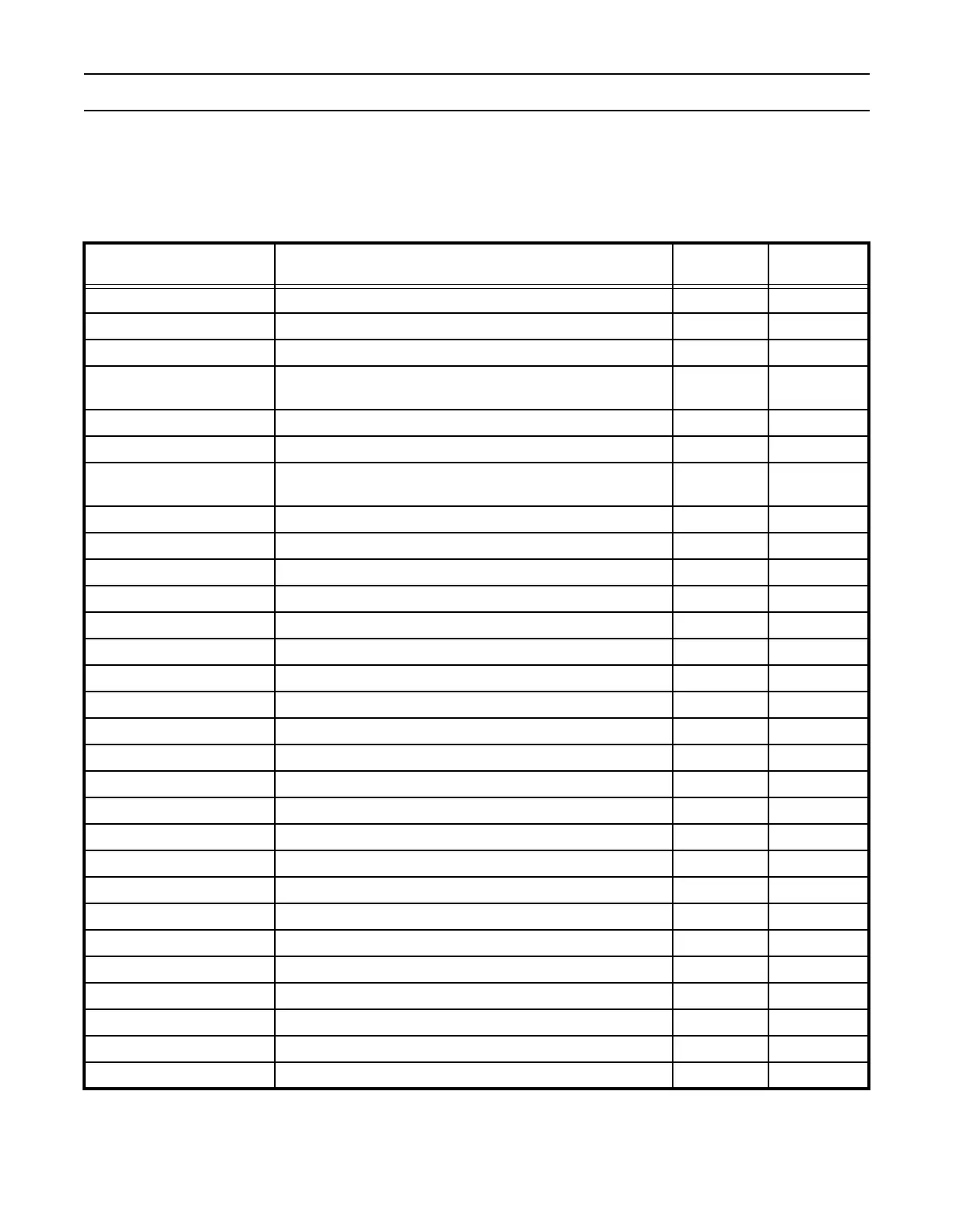

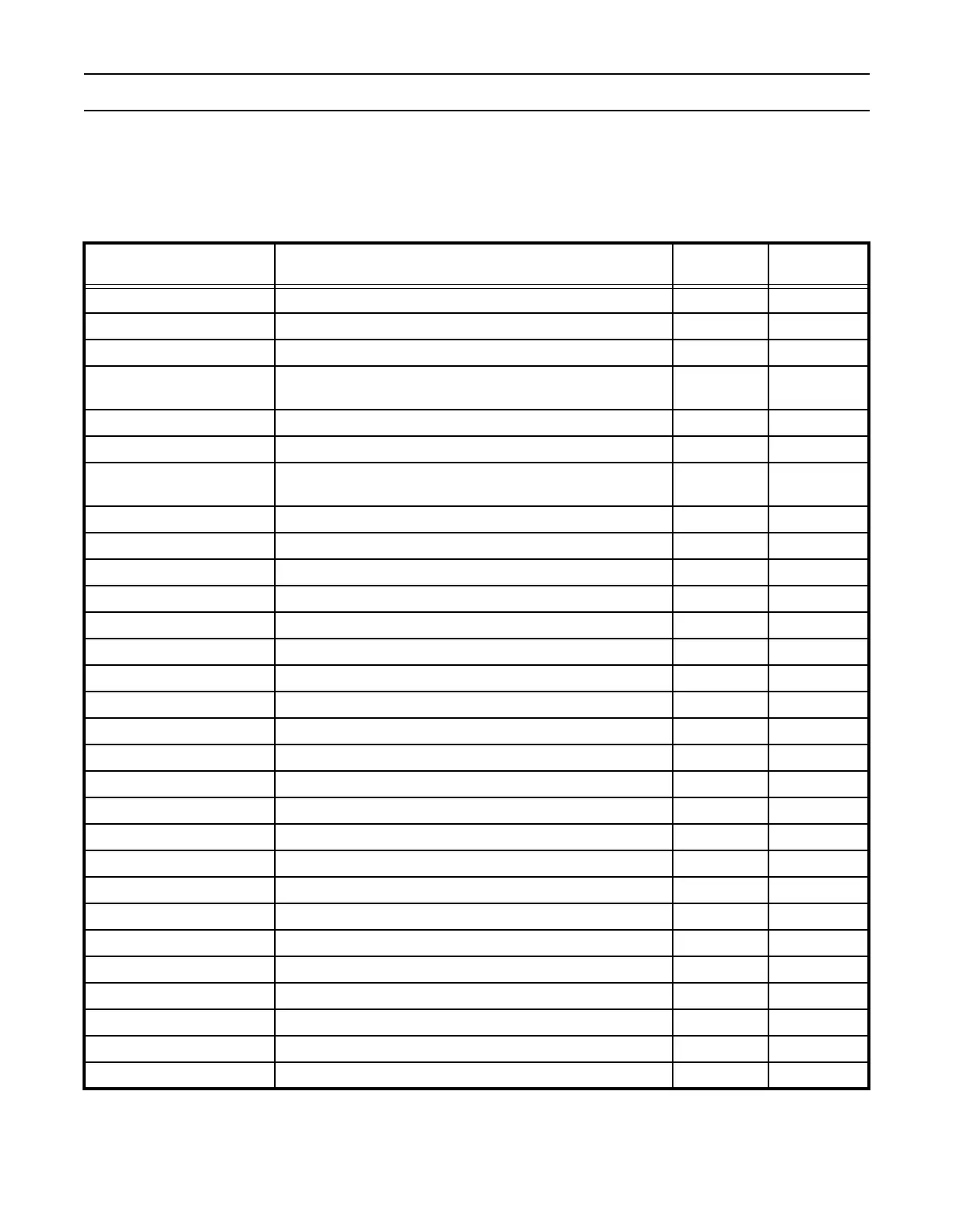

REGISTER DESCRIPTION

The ETM contains 29 registers as shown in Table 227. below. They are described in detail in the ARM IHI 0014E document

published by ARM Limited, which is available via the Internet at http://www.arm.com.

Table 227: ETM Registers

Name Description Access

Register

encoding

ETM Control Controls the general operation of the ETM Read/Write 000 0000

ETM Configuration Code Allows a debugger to read the number of each type of resource Read Only 000 0001

Trigger Event Holds the controlling event Write Only 000 0010

Memory Map Decode Control

Eight-bit register, used to statically configure the memory map

decoder

Write Only 000 0011

ETM Status Holds the pending overflow status bit Read Only 000 0100

System Configuration Holds the configuration information using the SYSOPT bus Read Only 000 0101

Trace Enable Control 3 Holds the trace on/off addresses

Write Only

000 0110

Trace Enable Control 2 Holds the address of the comparison Write Only 000 0111

Trace Enable Event Holds the enabling event Write Only 000 1000

Trace Enable Control 1 Holds the include and exclude regions Write Only 000 1001

FIFOFULL Region Holds the include and exclude regions Write Only 000 1010

FIFOFULL Level Holds the level below which the FIFO is considered full Write Only 000 1011

ViewData event Holds the enabling event Write Only 000 1100

ViewData Control 1 Holds the include/exclude regions Write Only 000 1101

ViewData Control 2 Holds the include/exclude regions Write Only 000 1110

ViewData Control 3 Holds the include/exclude regions Write Only 000 1111

Address Comparator 1 to 16 Holds the address of the comparison Write Only 001 xxxx

Address Access Type 1 to 16 Holds the type of access and the size Write Only 010 xxxx

reserved - - 000 xxxx

reserved - - 100 xxxx

Initial Counter Value 1 to 4 Holds the initial value of the counter Write Only 101 00xx

Counter Enable 1 to 4 Holds the counter clock enable control and event Write Only 101 01xx

Counter reload 1 to 4 Holds the counter reload event Write Only 101 10xx

Counter Value 1 to 4 Holds the current counter value Read Only 101 11xx

Sequencer State and Control Holds the next state triggering events. - 110 00xx

External Output 1 to 4 Holds the controlling events for each output Write Only 110 10xx

Reserved - - 110 11xx

Reserved - - 111 0xxx

Reserved - - 111 1xxx

Loading...

Loading...