System Control Block 70 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

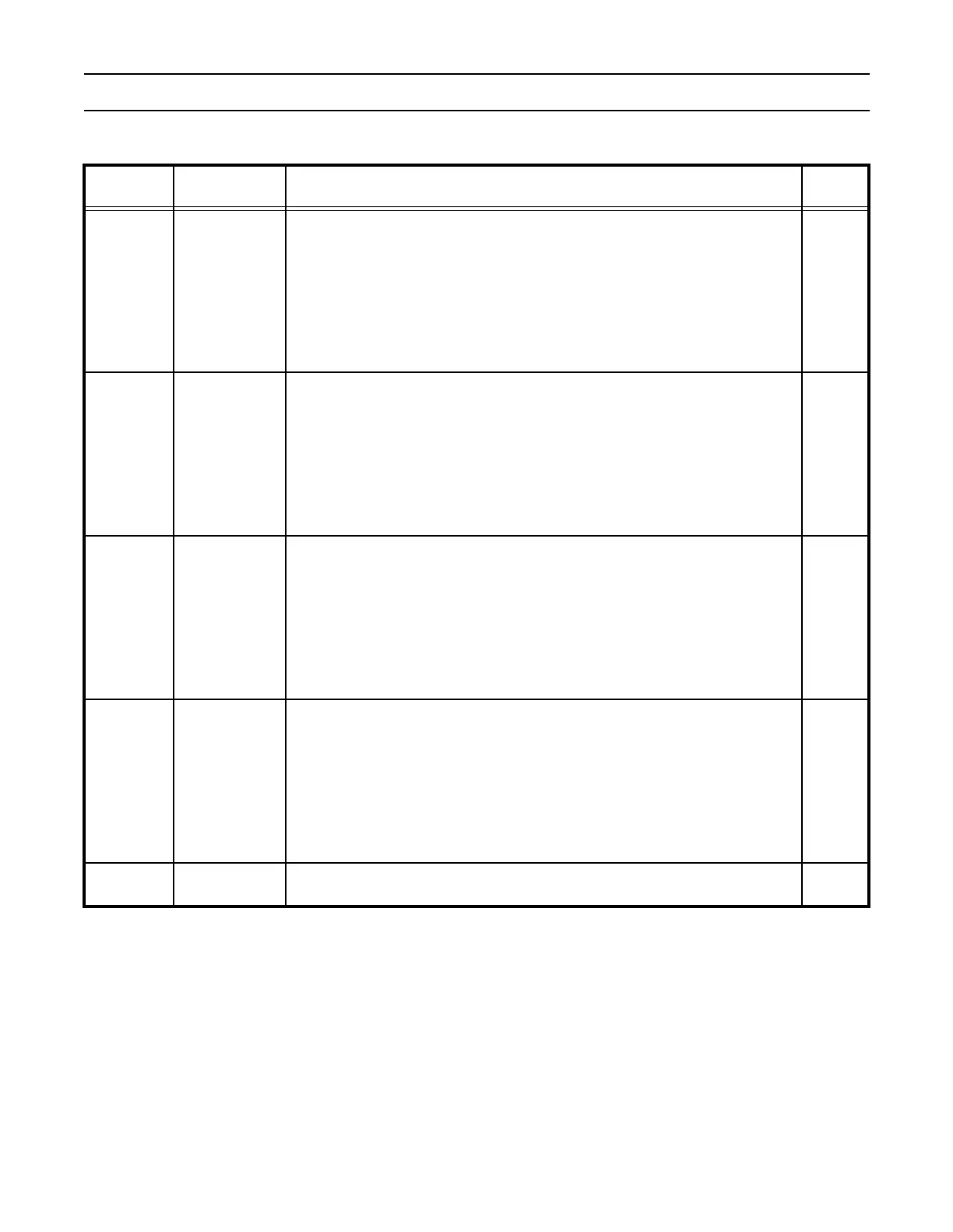

External Interrupt Wakeup Register (EXTWAKE - 0xE01FC144)

Enable bits in the EXTWAKE register allow the external interrupts to wake up the processor if it is in Power Down mode. The

related EINTn function must be mapped to the pin in order for the wakeup process to take place. It is not necessary for the

interrupt to be enabled in the Vectored Interrupt Controller for a wakeup to take place. This arrangement allows additional

capabilities, such as having an external interrupt input wake up the processor from Power Down mode without causing an

interrupt (simply resuming operation), or allowing an interrupt to be enabled during Power Down without waking the processor

up if it is asserted (eliminating the need to disable the interrupt if the wakeup feature is not desirable in the application).

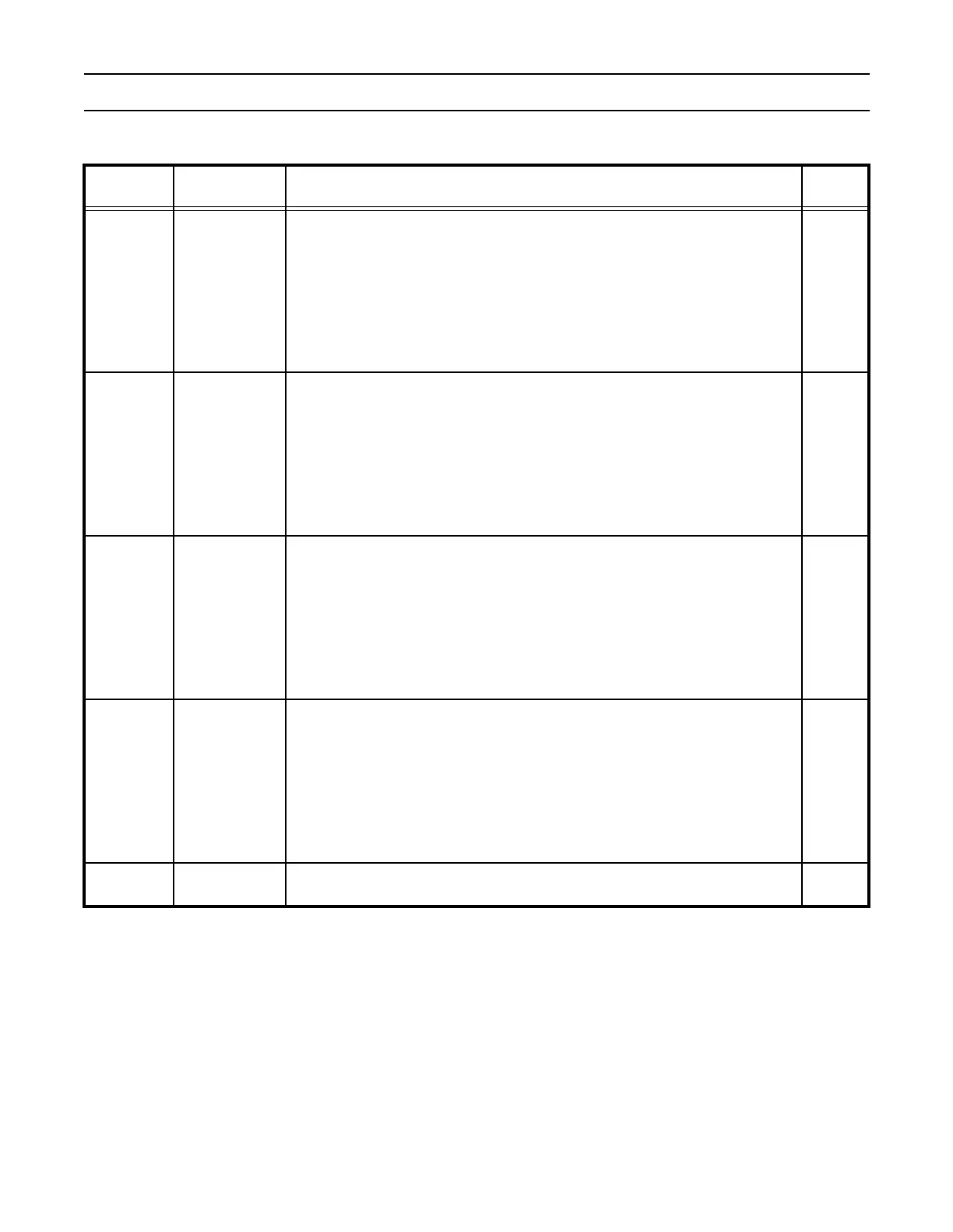

Table 15: External Interrupt Flag Register (EXTINT - 0xE01FC140)

EXTINT Function Description

Reset

Value

0EINT0

In level-sensitive mode, this bit is set if the EINT0 function is selected for its pin, and

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT0

function is selected for its pin, and the selected edge occurs on the pin.

Up to two pins can be selected to perform EINT0 function (see P0.1 and P0.16

description in "Pin Configuration" chapter.)

This bit is cleared by writing a one to it, except in level sensitive mode when the pin

is in its active state.

0

1EINT1

In level-sensitive mode, this bit is set if the EINT1 function is selected for its pin, and

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT1

function is selected for its pin, and the selected edge occurs on the pin.

Up to two pins can be selected to perform EINT1 function (see P0.3 and P0.14

description in "Pin Configuration" chapter.)

This bit is cleared by writing a one to it, except in level sensitive mode when the pin

is in its active state.

0

2EINT2

In level-sensitive mode, this bit is set if the EINT2 function is selected for its pin, and

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT2

function is selected for its pin, and the selected edge occurs on the pin.

Up to two pins can be selected to perform EINT2 function (see P0.7 and P0.15

description in "Pin Configuration" chapter.)

This bit is cleared by writing a one to it, except in level sensitive mode when the pin

is in its active state.

0

3EINT3

In level-sensitive mode, this bit is set if the EINT3 function is selected for its pin, and

the pin is in its active state. In edge-sensitive mode, this bit is set if the EINT3

function is selected for its pin, and the selected edge occurs on the pin.

Up to three pins can be selected to perform EINT3 function (see P0.9, P0.20 and

P0.30 description in "Pin Configuration" chapter.)

This bit is cleared by writing a one to it, except in level sensitive mode when the pin

is in its active state.

0

7:4 Reserved

Reserved, user software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

NA

Loading...

Loading...