Pulse Width Modulator (PWM) 235 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

PWM Control Register (PWMPCR - 0xE001404C)

The PWM Control Register is used to enable and select the type of each PWM channel. The function of each of the bits are shown

in Table 170.

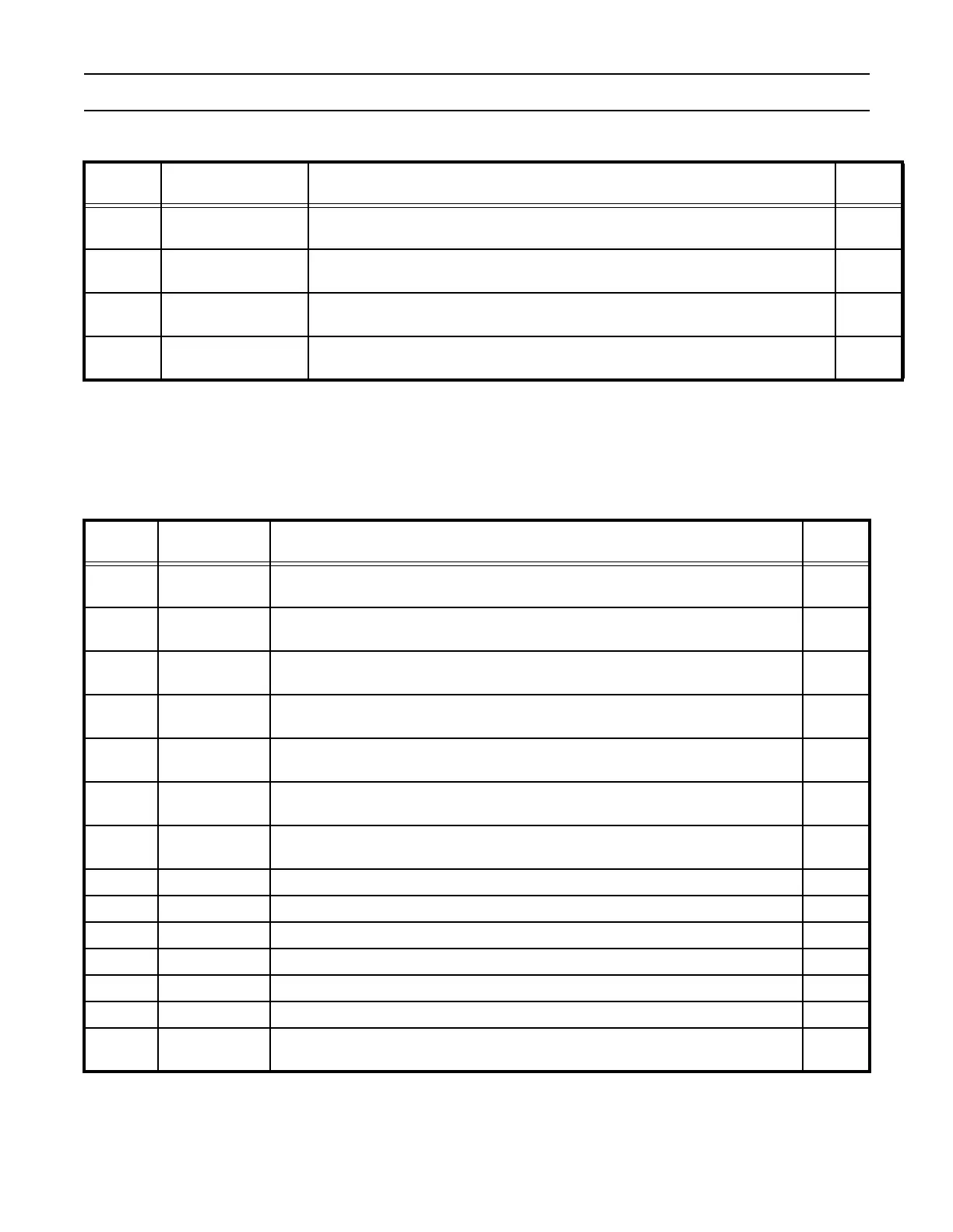

17 Stop on PWMMR5

When one, the PWMTC and PWMPC will be stopped and PWMTCR[0] will be set to

0 if PWMMR5 matches the PWMTC. When zero this feature is disabled

0

18 Interrupt on PWMMR6

When one, an interrupt is generated when PWMMR6 matches the value in the

PWMTC. When zero this interrupt is disabled.

0

19 Reset on PWMMR6

When one, the PWMTC will be reset if PWMMR6 matches it. When zero this feature

is disabled.

0

20 Stop on PWMMR6

When one, the PWMTC and PWMPC will be stopped and PWMTCR[0] will be set to

0 if PWMMR6 matches the PWMTC. When zero this feature is disabled

0

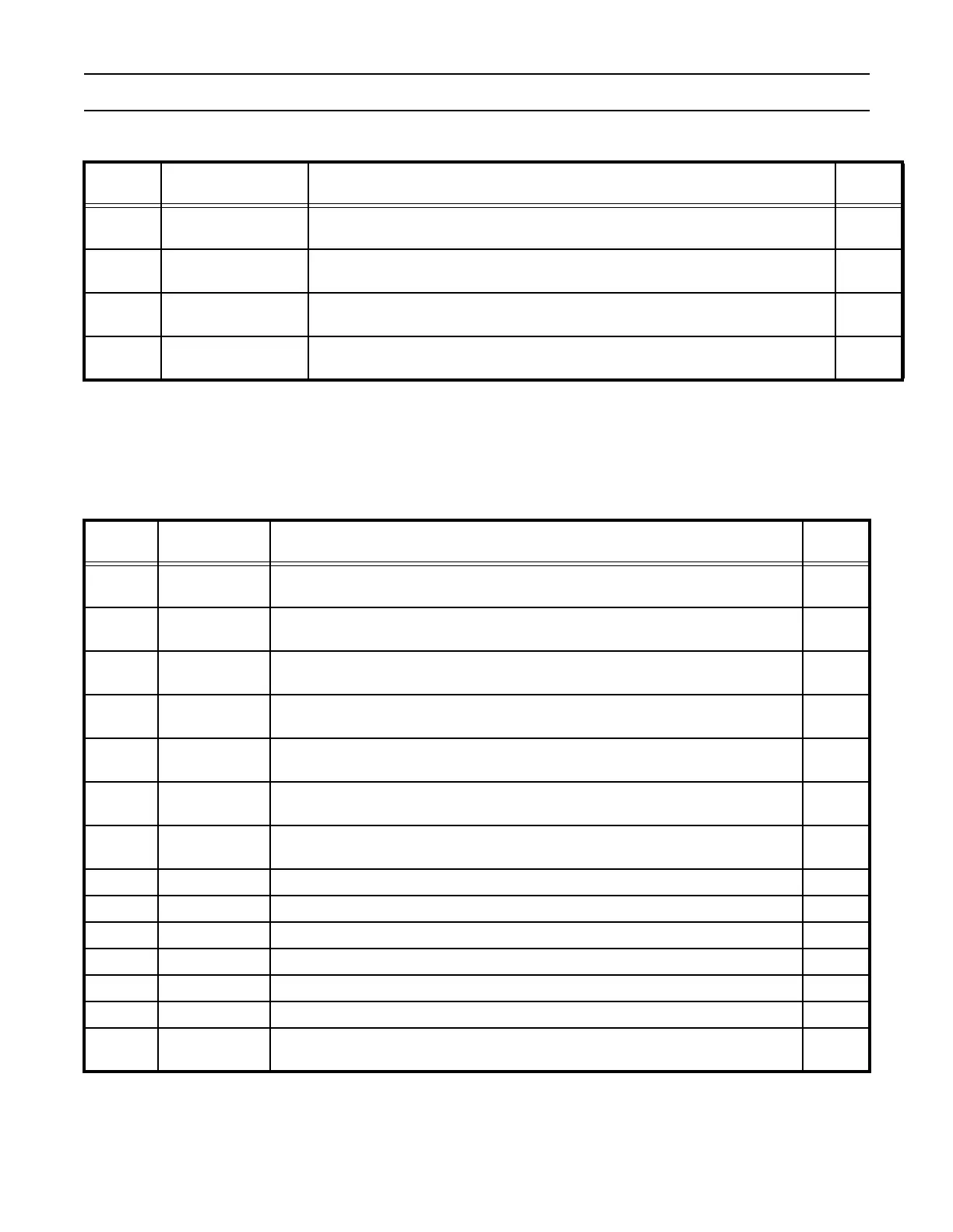

Table 170: PWM Control Register (PWMPCR - 0xE001404C)

PWMPCR Function Description

Reset

Value

1:0 Reserved

Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

2 PWMSEL2

When zero, selects single edge controlled mode for PWM2. When one, selects double

edge controlled mode for the PWM2 output.

0

3 PWMSEL3

When zero, selects single edge controlled mode for PWM3. When one, selects double

edge controlled mode for the PWM3 output.

0

4 PWMSEL4

When zero, selects single edge controlled mode for PWM4. When one, selects double

edge controlled mode for the PWM4 output.

0

5 PWMSEL5

When zero, selects single edge controlled mode for PWM5. When one, selects double

edge controlled mode for the PWM5 output.

0

6 PWMSEL6

When zero, selects single edge controlled mode for PWM6. When one, selects double

edge controlled mode for the PWM6 output.

0

8:7 Reserved

Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

9 PWMENA1 When one, enables the PWM1 output. When zero, disables the PWM1 output. 0

10 PWMENA2 When one, enables the PWM2 output. When zero, disables the PWM2 output. 0

11 PWMENA3 When one, enables the PWM3 output. When zero, disables the PWM3 output. 0

12 PWMENA4 When one, enables the PWM4 output. When zero, disables the PWM4 output. 0

13 PWMENA5 When one, enables the PWM5 output. When zero, disables the PWM5 output. 0

14 PWMENA6 When one, enables the PWM6 output. When zero, disables the PWM6 output. 0

15 Reserved

Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

Table 169: PWM Match Control Register (PWMMCR - 0xE0014014)

PWMMCR Function Description

Reset

Value

Loading...

Loading...