Real Time Clock 255 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

Prescaler Operation

The Prescaler block labelled "Combination Logic" in Figure 45 determines when the decrement of the 13-bit PREINT counter is

extended by one pclk. In order to both insert the correct number of longer cycles, and to distribute them evenly, the Combinatorial

Logic associates each bit in PREFRAC with a combination in the 15-bit Fraction Counter. These associations are shown in (???).

For example, if PREFRAC bit 14 is a one (representing the fraction 1/2), then half of the cycles counted by the 13-bit counter

need to be longer. When there is a 1 in the LSB of the Fraction Counter, the logic causes every alternate count (whenever the

LSB of the Fraction Counter=1) to be extended by one pclk, evenly distributing the pulse widths. Similarly, a one in PREFRAC

bit 13 (representing the fraction 1/4) will cause every fourth cycle (whenever the two LSBs of the Fraction Counter=10) counted

by the 13-bit counter to be longer.

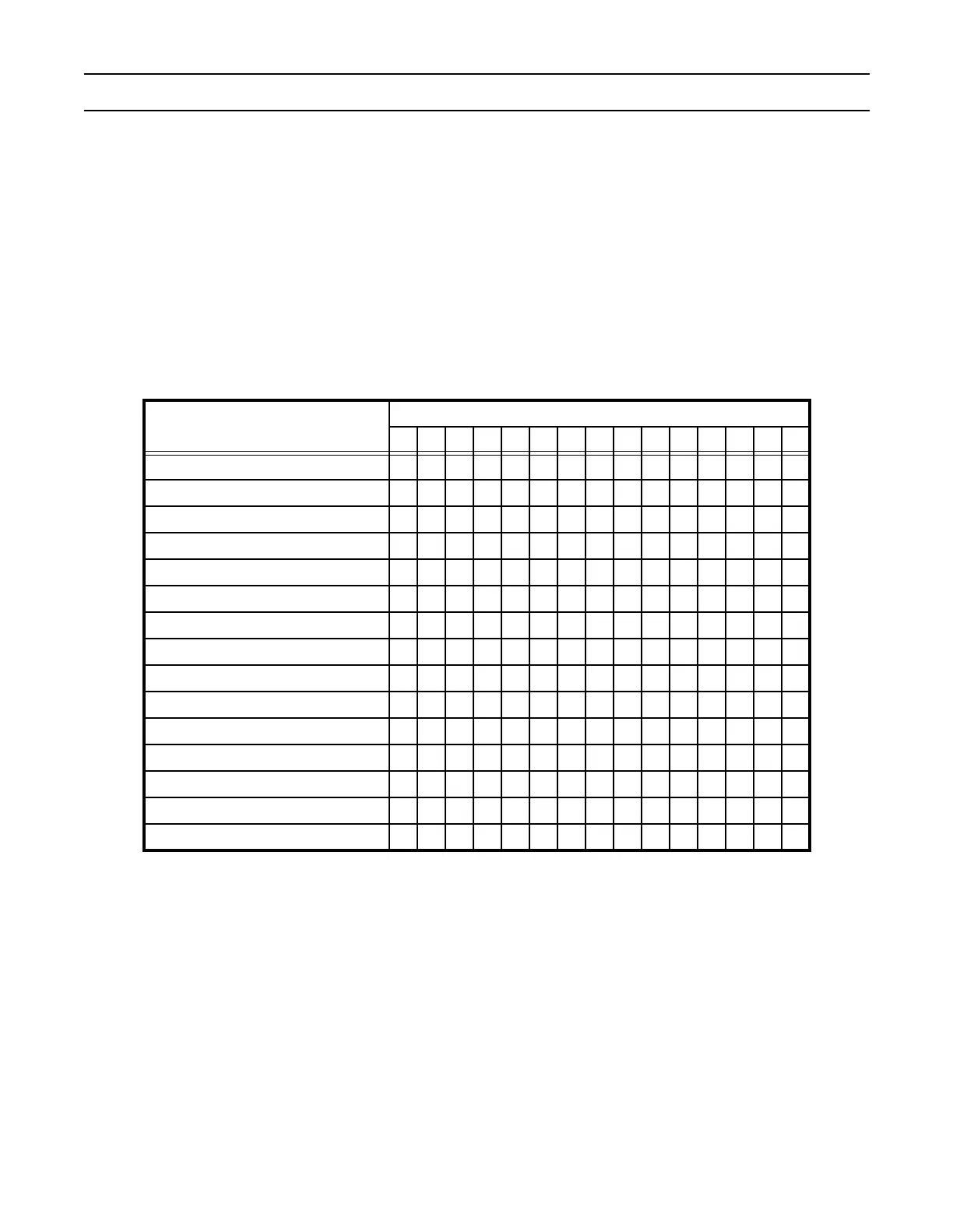

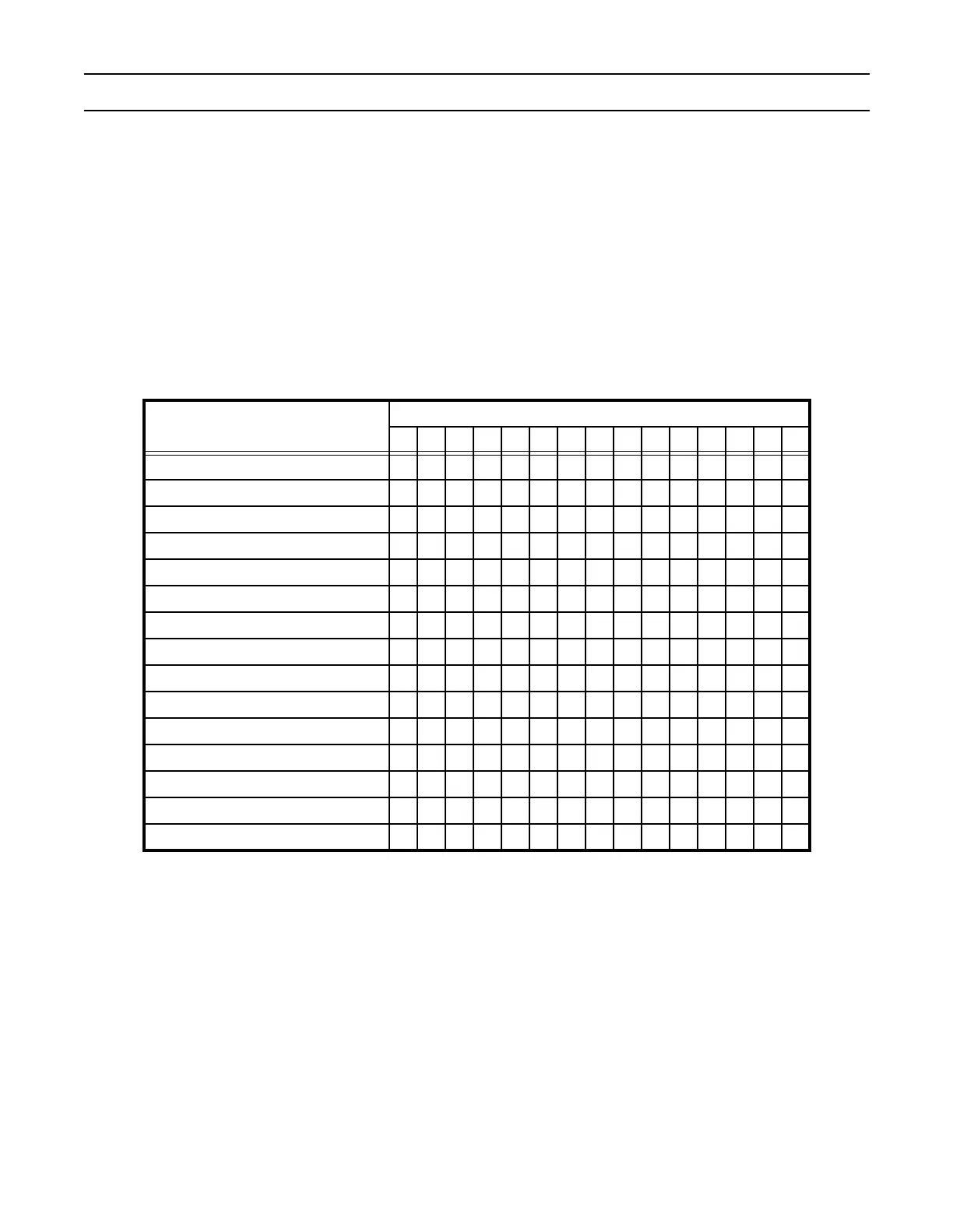

Table 192: Prescaler cases where the Integer Counter reload value is incremented

Fraction Counter

PREFRAC Bit

14131211109876543210

--- ---- ---- ---1 1--------------

--- ---- ---- --10 -1-------------

--- ---- ---- -100 --1------------

--- ---- ---- 1000 ---1-----------

--- ---- ---1 0000 ----1----------

--- ---- --10 0000 -----1---------

--- ---- -100 0000 ------1--------

--- ---- 1000 0000 -------1-------

--- ---1 0000 0000 --------1------

--- --10 0000 0000 ---------1-----

--- -100 0000 0000 ----------1----

--- 1000 0000 0000 -----------1---

--1 0000 0000 0000 ------------1--

-10 0000 0000 0000 -------------1-

100 0000 0000 0000 --------------1

Loading...

Loading...