Date Code 20080110 Analyzing Events 9-11

SEL-387E Instruction Manual

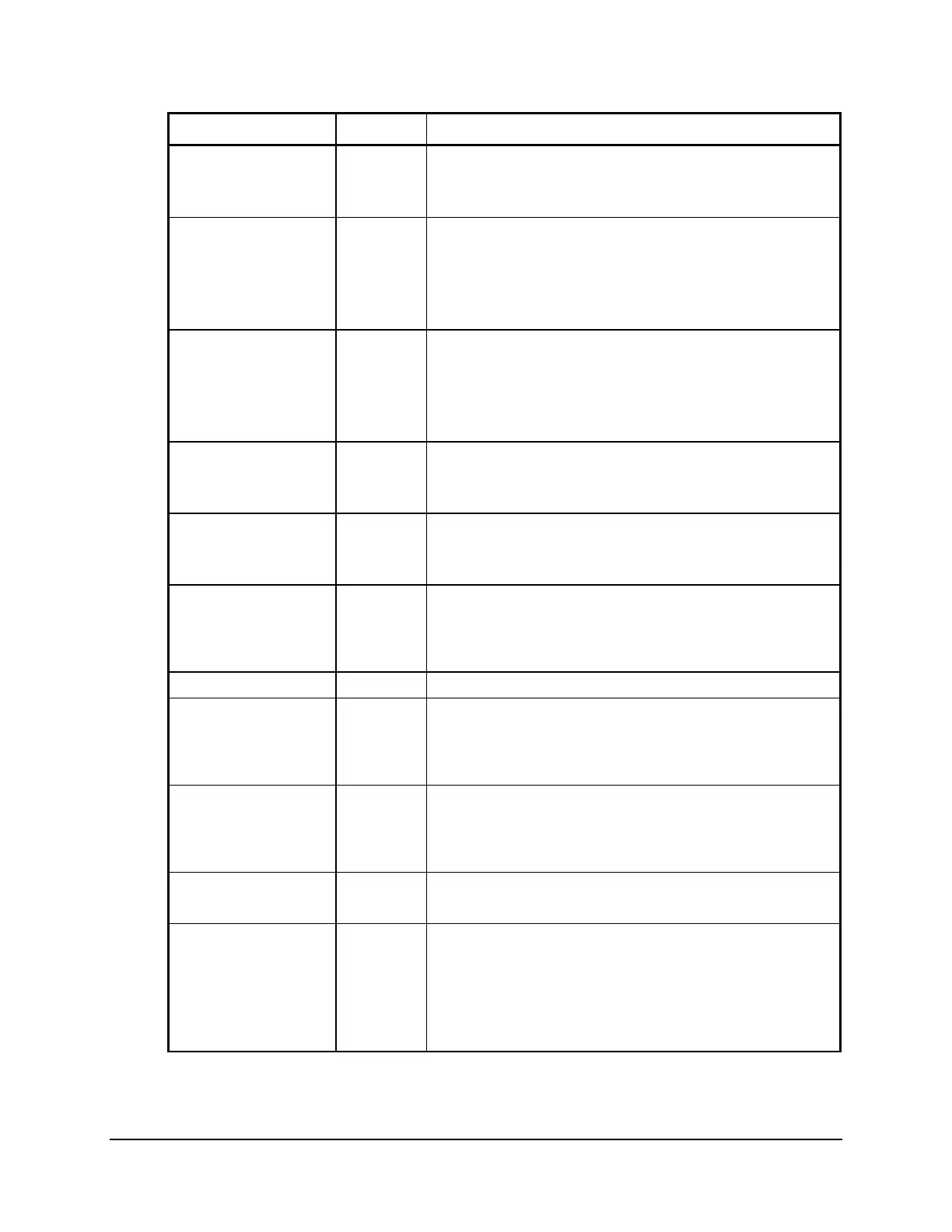

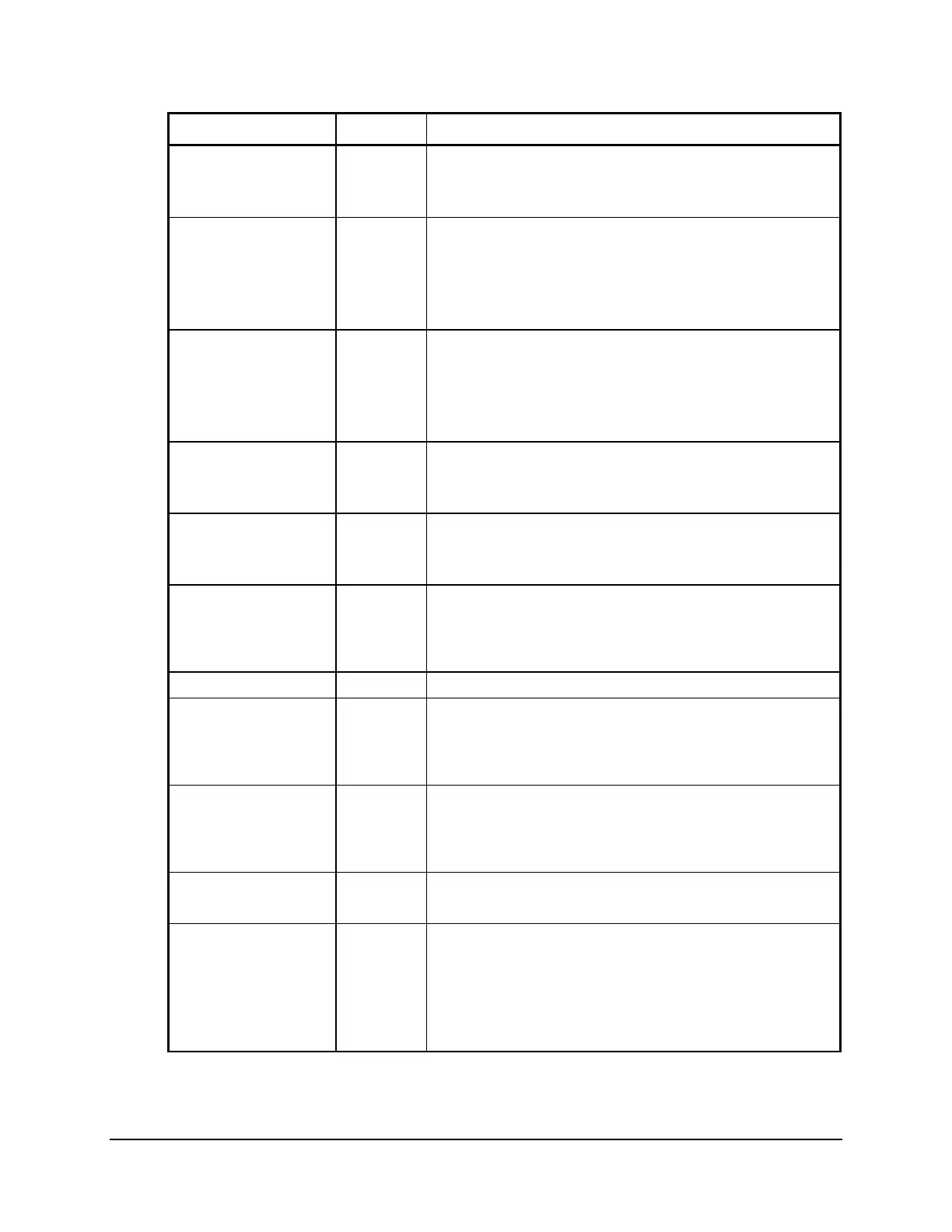

Column Heading Symbol Definition

Use same logic for

overcurrent elements

in Wdg 2 and Wdg 3.

51PC1 p

T

r

1

.

51PC1 asserted

51PC1T asserted

Timing to reset (51PC1RS=Y)

Timing to reset after 51PC1T assertion (51PC1RS=N)

51PC1R asserted

51NC1 p

T

r

1

.

51NC1 asserted

51NC1T asserted

Timing to reset (51NC1RS=Y)

Timing to reset after 51NC1T assertion (51NC1RS=N)

51NC1R asserted

24D1 1

D

24D1 element picked up

24D1 element picked up; timer timed out on pickup time;

timer output 24D1T asserted

24C2 2

C

r

24C2 element picked up and timing

24C2 element timed out

24C2 element fully reset

27P 1

2

b

L 1 instantaneous phase undervoltage element picked up

L 2 instantaneous phase undervoltage element picked up

Both Level 1 and Level 2 phase undervoltage elements

picked up

27V1 V 27V1 positive-sequence undervoltage element picked up

27PP 1

2

b

Level 1 phase-to-phase undervoltage element picked up

Level 2 phase-to-phase undervoltage element picked up

Both Level 1 and Level 2 phase-to-phase undervoltage

elements picked up

59P 1

2

b

L 1 instantaneous phase overvoltage element picked up

L 2 instantaneous phase overvoltage element picked up

Both Level 1 and Level 2 phase overvoltage elements

picked up

59V1 V Positive-sequence instantaneous overvoltage element

59V1 picked up

59PP 1

2

b

Level 1 phase-to-phase instantaneous overvoltage

element picked up

Level 2 phase-to-phase instantaneous overvoltage

element picked up

Both phase-to-phase instantaneous overvoltage elements

picked up

Loading...

Loading...