24 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 1: Introduction to the RocketIO GTP Transceiver

R

Table 1-3 summarizes all GTP_DUAL ports and provides links to their detailed

descriptions.

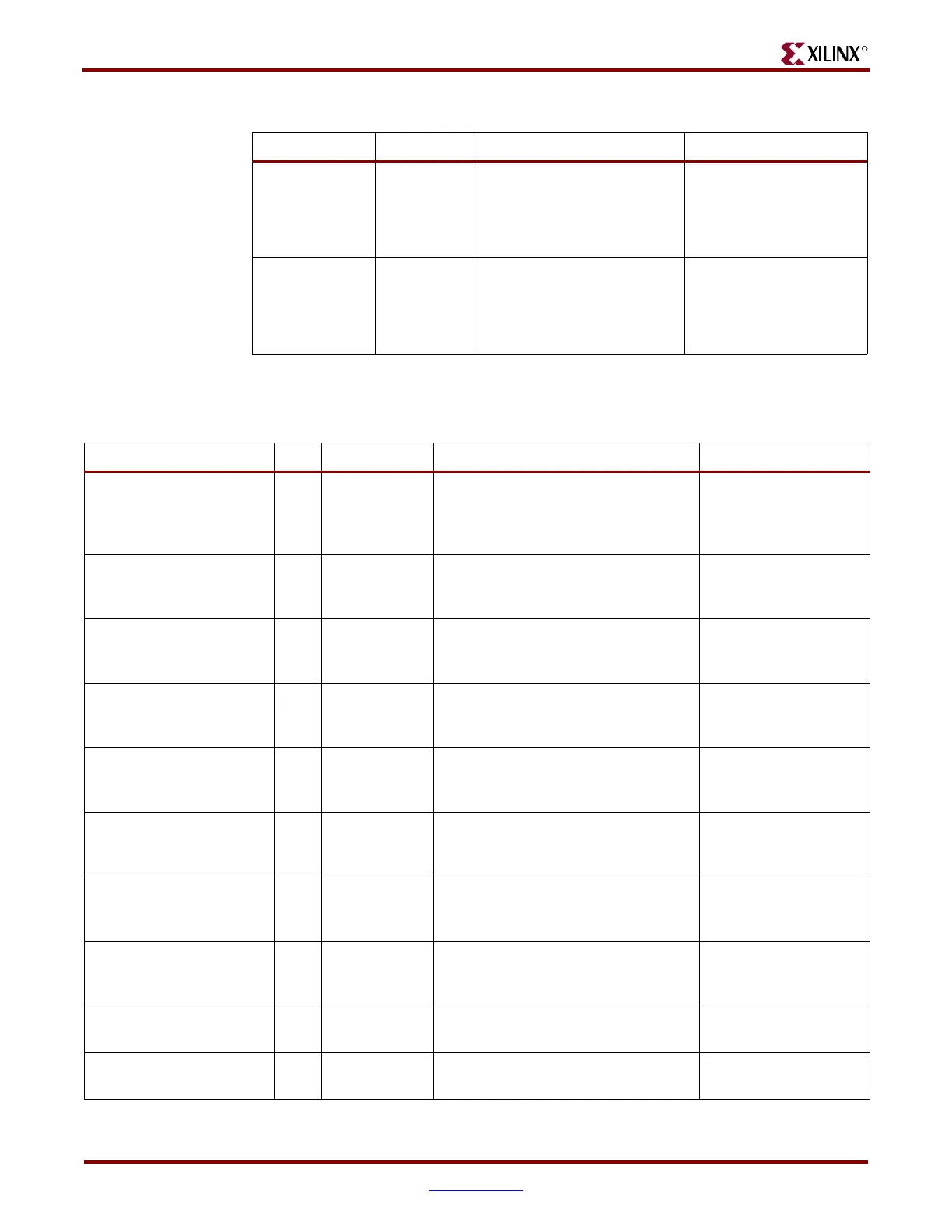

MGTRXN0

MGTRXP0

MGTRXN1

MGTRXP1

In

Differential complements

forming a differential receiver

input pair for each transceiver.

RX Termination and

Equalization (page 125)

MGTTXN0

MGTTXP0

MGTTXN1

MGTTXP1

In Pad

Differential complements

forming a differential

transmitter output pair for

each transceiver.

Configurable TX Driver

(page 113)

Table 1-2: GTP_DUAL Analog Pin Summary (Continued)

Pin Dir Description Section (Page)

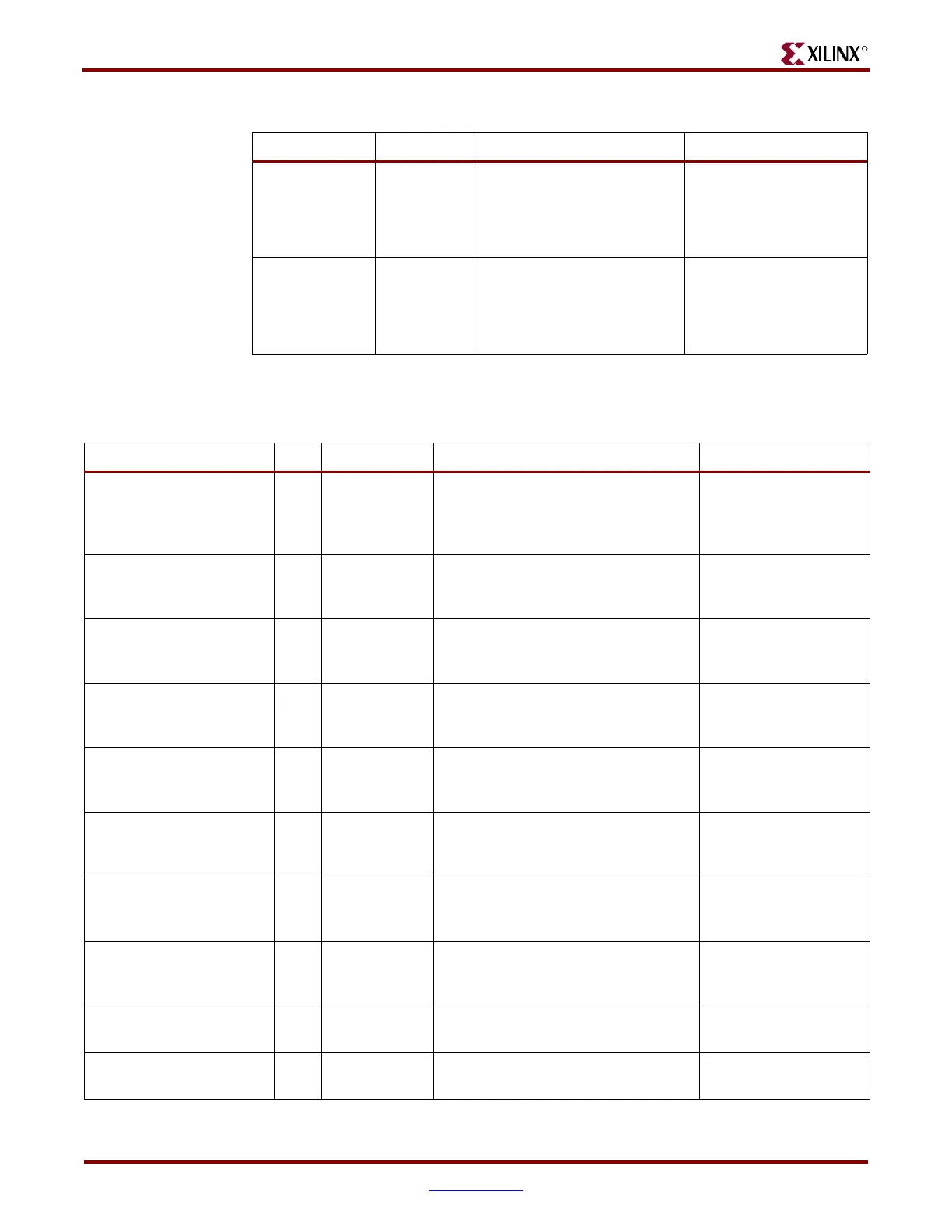

Table 1-3: GTP_DUAL Port Summary

Port Dir Domain Description Section (Page)

CLKIN In Async

Reference clock input to the shared

PMA PLL.

Shared PMA PLL

(page 61), Clocking

(page 70), Power

Control (page 81)

DADDR[6:0] In DCLK DRP address bus.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DCLK In N/A DRP interface clock.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DEN In DCLK Enables DRP read or write operations.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DI[15:0] In DCLK

Data bus for writing configuration data

from the FPGA fabric to the

GTP_DUAL tile.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DO[15:0] Out DCLK

Data bus for reading configuration data

from the GTP_DUAL tile to the FPGA

fabric.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DRDY Out DCLK

Indicates the operation is complete

for DRP write

operations and data is

valid for DRP read operations.

Dynamic

Reconfiguration Port

(DRP) (page 87)

DWE In DCLK

Indicates whether the DRP operation is

a read or a write.

Dynamic

Reconfiguration Port

(DRP) (page 87)

GTPRESET In Async

Starts the full GTP_DUAL reset

sequence.

Reset (page 73)

GTPTEST[3:0] In Async

Factory test pins. Must be strapped

Low for normal operation.

Loading...

Loading...