Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 27

UG196 (v1.3) May 25, 2007

Ports and Attributes

R

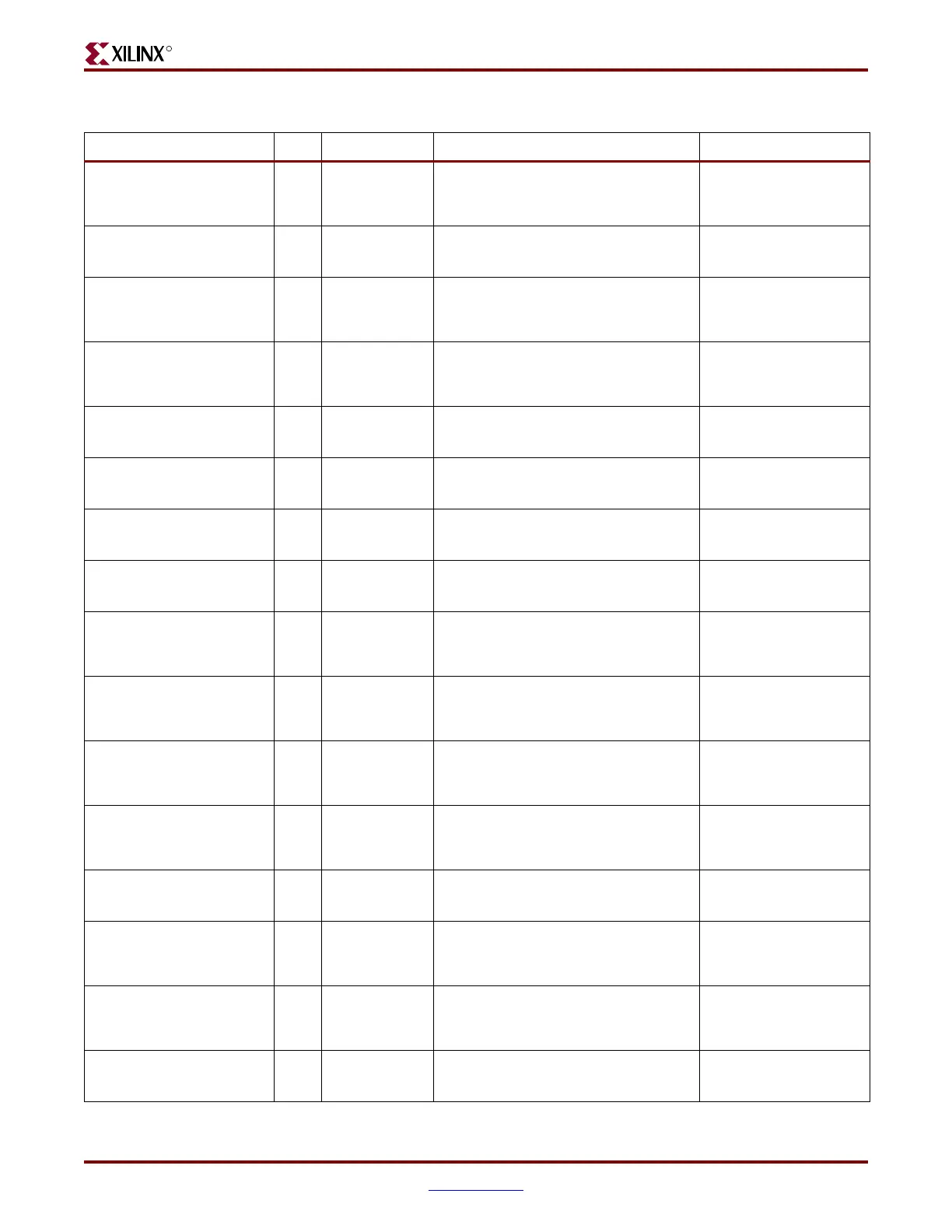

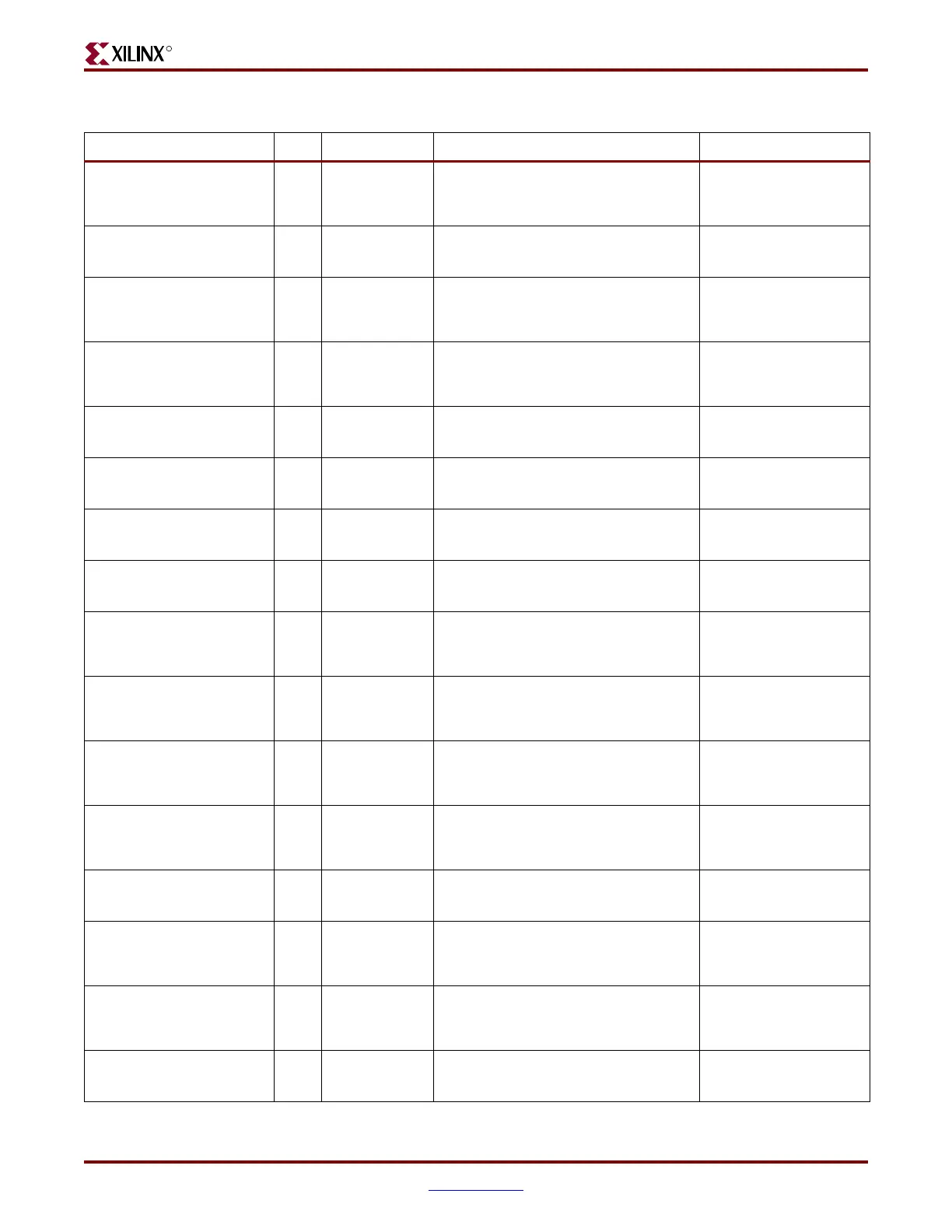

RXCHBONDO0[2:0]

RXCHBONDO1[2:0]

Out RXUSRCLK FPGA channel bonding control.

Configurable Channel

Bonding (Lane Deskew)

(page 176)

RXCLKCORCNT0[2:0]

RXCLKCORCNT1[2:0]

Out RXUSRCLK2

Reports the status of the elastic buffer

clock correction.

Configurable Clock

Correction (page 169)

RXCOMMADET0

RXCOMMADET1

Out RXUSRCLK2

Asserted when the comma alignment

block detects a comma.

Configurable Comma

Alignment and

Detection (page 150)

RXCOMMADETUSE0

RXCOMMADETUSE1

In RXUSRCLK2

Activates the comma detection and

alignment circuit.

Configurable Comma

Alignment and

Detection (page 150)

RXDATA0

RXDATA1

Out RXUSRCLK2

Receive data bus of the receive interface

to the FPGA.

FPGA RX Interface

(page 182)

RXDATAWIDTH0

RXDATAWIDTH1

In RXUSRCLK2

Selects the width of the RXDATA

receive data connection to the FPGA.

FPGA RX Interface

(page 182)

RXDEC8B10BUSE0

RXDEC8B10BUSE1

In RXUSRCLK2 Enables the 8B/10B decoder.

Configurable 8B/10B

Decoder (page 157)

RXDISPERR0[1:0]

RXDISPERR1[1:0]

Out RXUSRCLK2

Indicates if RXDATA was received with

a disparity error.

Configurable 8B/10B

Decoder (page 157)

RXELECIDLE0

RXELECIDLE1

Out RXUSRCLK2

Indicates the differential voltage

between RXN and RXP dropped below

the minimum threshold.

RX OOB/Beacon

Signaling (page 130)

RXELECIDLERESET0

RXELECIDLERESET1

In Async

Resets the RX Clock Data Recovery

circuit, used by the mandatory link idle

reset circuit.

Reset (page 73), RX

Clock Data Recovery

(CDR) (page 136)

RXENCHANSYNC0

RXENCHANSYNC1

In RXUSRCLK2 Enables channel bonding.

Configurable Channel

Bonding (Lane Deskew)

(page 176)

RXENELECIDLERESETB In Async

Enables the RXELECIDLERESET

inputs, used by the mandatory Link

Idle Reset circuit (active Low).

Reset (page 73), RX

Clock Data Recovery

(CDR) (page 136)

RXENEQB0

RXENEQB1

In Async

Enables receiver equalization (active

Low).

RX Termination and

Equalization (page 125)

RXENMCOMMAALIGN0

RXENMCOMMAALIGN1

In RXUSRCLK2

Aligns the byte boundary when comma

minus is detected.

Configurable Comma

Alignment and

Detection (page 150)

RXENPCOMMAALIGN0

RXENPCOMMAALIGN1

In RXUSRCLK2

Aligns the byte boundary when comma

plus is detected.

Configurable Comma

Alignment and

Detection (page 150)

RXENPRBSTST0[1:0]

RXENPRBSTST1[1:0]

In RXUSRCLK2 Receiver test pattern checker control.

PRBS Detection

(page 147)

Table 1-3: GTP_DUAL Port Summary (Continued)

Port Dir Domain Description Section (Page)

Loading...

Loading...