6243/44 DC Voltage Current Source/Monitor Operation Manual

5.2.8 Status Byte

5-14

This register responds to the serial poll from the controller. When responding to the serial poll, the

Status Byte Register’s bit 0 to 5, bit 7 and RQS are read out, after which RQS is reset to 0.

Other bits are not cleared until their factors become 0.

The Status Byte Register, RQS, and MSS can be cleared by executing “*CLS.”

Accompanying this, the SRQ line also becomes false.

Table 5-1 shows the meaning of each of the Status Byte Register’s bits.

Common conditions on which the Status Byte Register is cleared

• Everything is cleared when the power is turned OFF and ON.

• *CLS clears everything except that MAV is not cleared if data exist in the output buffer.

• When all the bits in DSB, MAV, and ESB are cleared

• Not cleared even if read out by *STB?

Conditions on which the Status Byte Enable Register is cleared

• When the power is turned OFF and ON

• When the *SRE0 command is executed

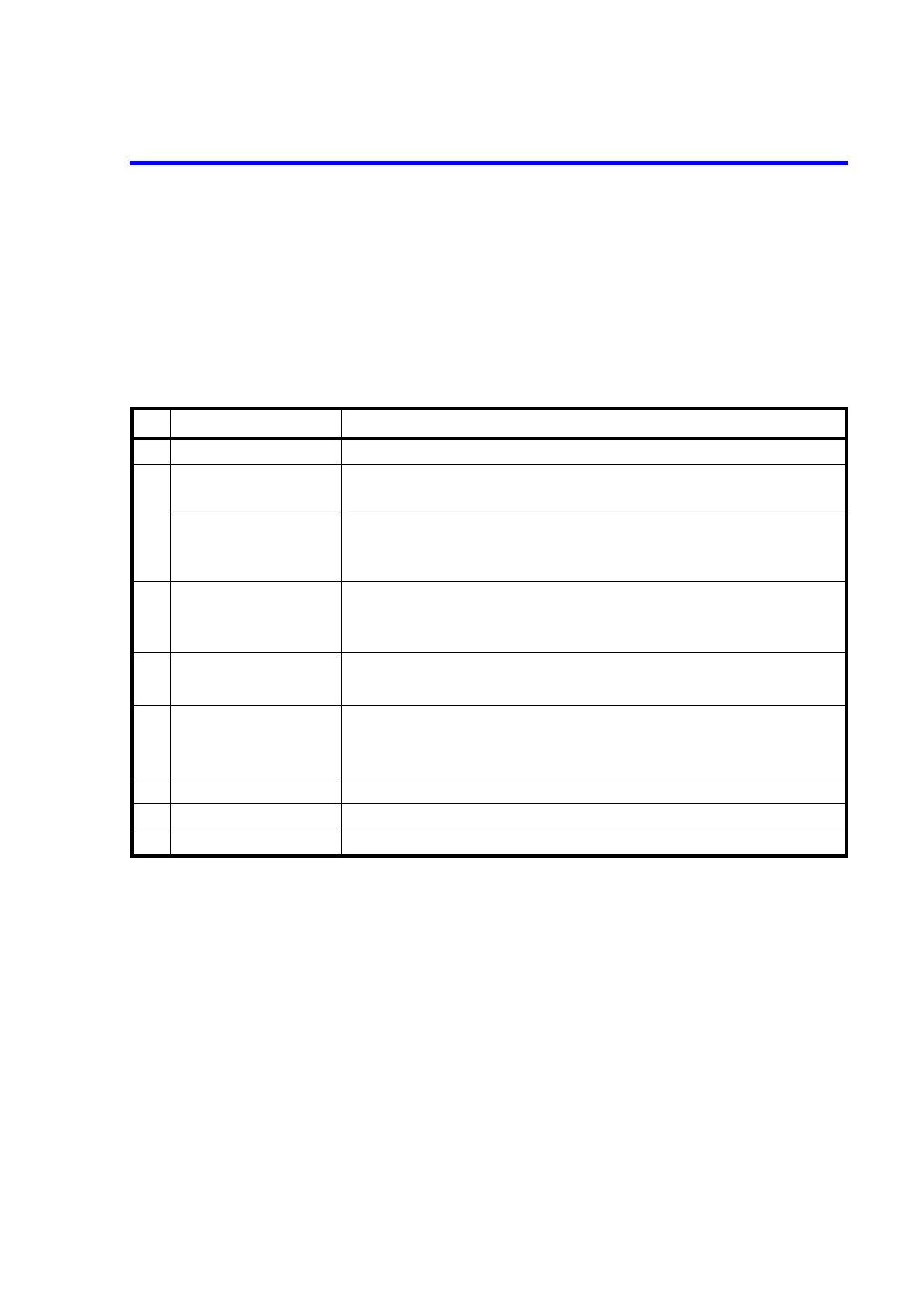

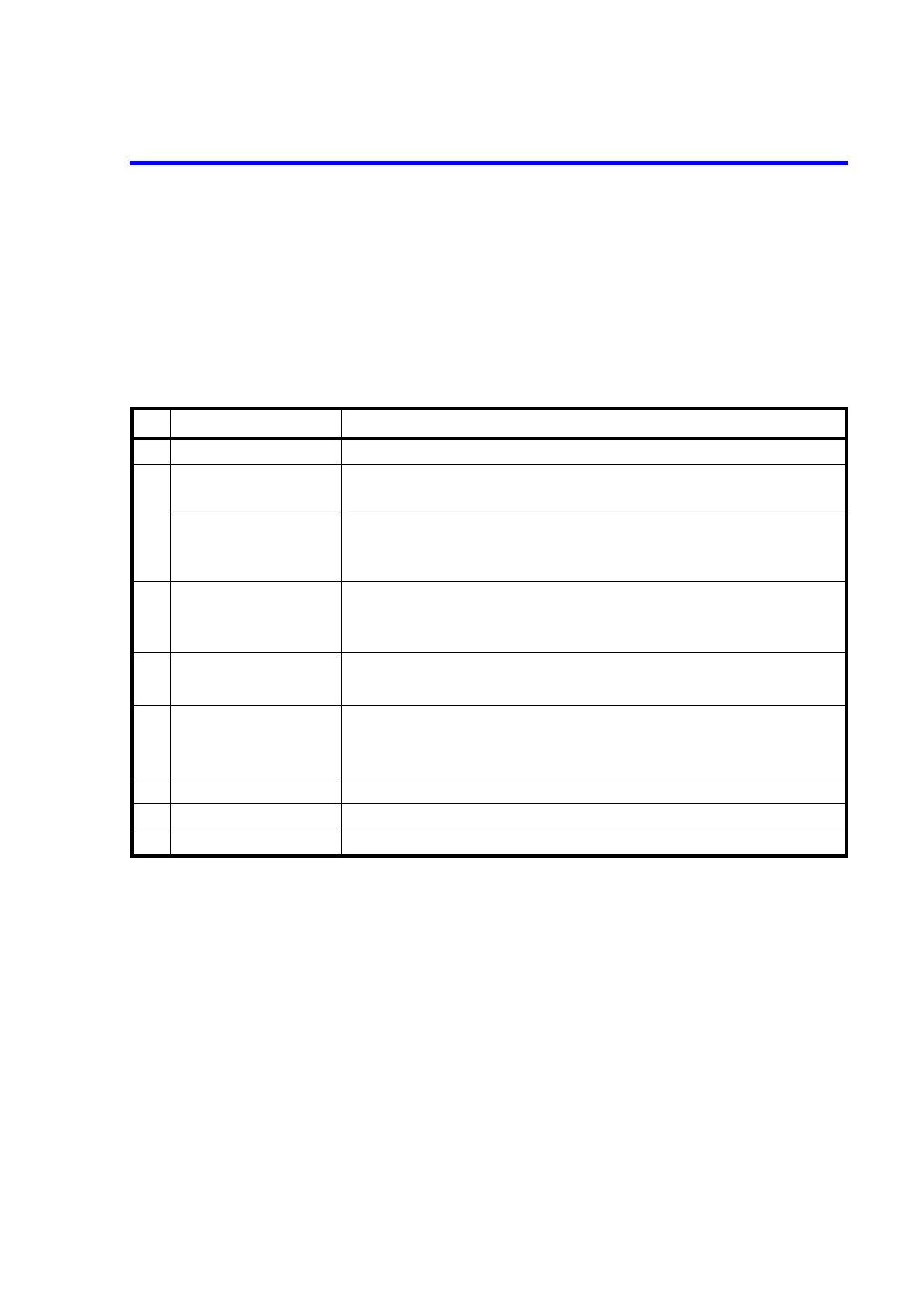

Table 5-1 Status Byte Register

bit Function definition Description

7 Not used. Always set to 0.

6MSS

Master Summary

ON: When a factor occurs in either STB, bit 6 is set to 1 if the bit correspond-

ing to SRER is set to 1.

RQS

Request Service

ON: MSS is set to 1. Accordingly RQS is set to 1. If the service request is set

to ON at this point, SRQ is sent.

OFF: When STB is read out with the serial poll.

5ESB

Standard Event Status

ON: When a factor occurs in SESR and 1 is set, this bit is set to 1 if the bit

corresponding to SESER is set to 1.

OFF: When SESR is cleared by reading out (*ESR?), bit 5 is set to 0.

4MAV

Message Available

ON: When output data is entered in the output buffer, bit 4 is set to 1.

OFF: When the output buffer is read out and become empty, this bit is set to 0.

3DSB

Device Event Status

ON: When a factor occurs in DESR and 1 is set, this bit is set to 1 if the bit

corresponding to DESER is set to 1.

OFF: When DESR is cleared by reading out (*DSR?), bit 3 is set to 0.

2 Not used. Always set to 0.

1 Not used. Always set to 0.

0 Not used. Always set to 0.

Loading...

Loading...