BL702/704/706 Reference Manual

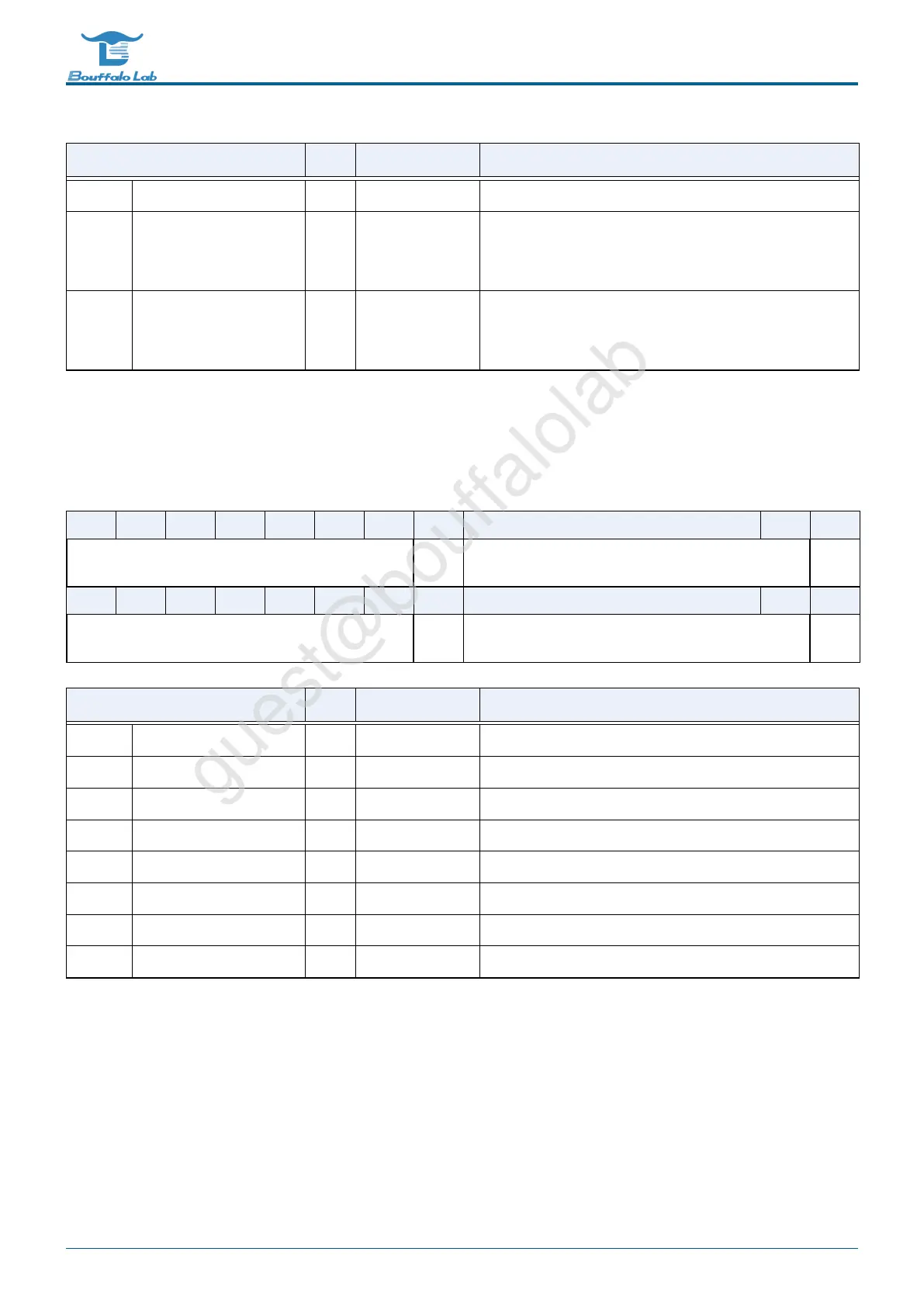

Bits

Name Type Reset Description

2 TXMDEN R/W 1’b0 Enable signal of output modulation

1 TXOEN R/W 1’b0 Output inverse signal

1’b0: Output stays at Low during idle state

1’b1: Output stays at High during idle state

0 TXEN R/W 1’b0 Enable signal of IRTX function

Asserting this bit will trigger the transaction, and should be

de-asserted after finish

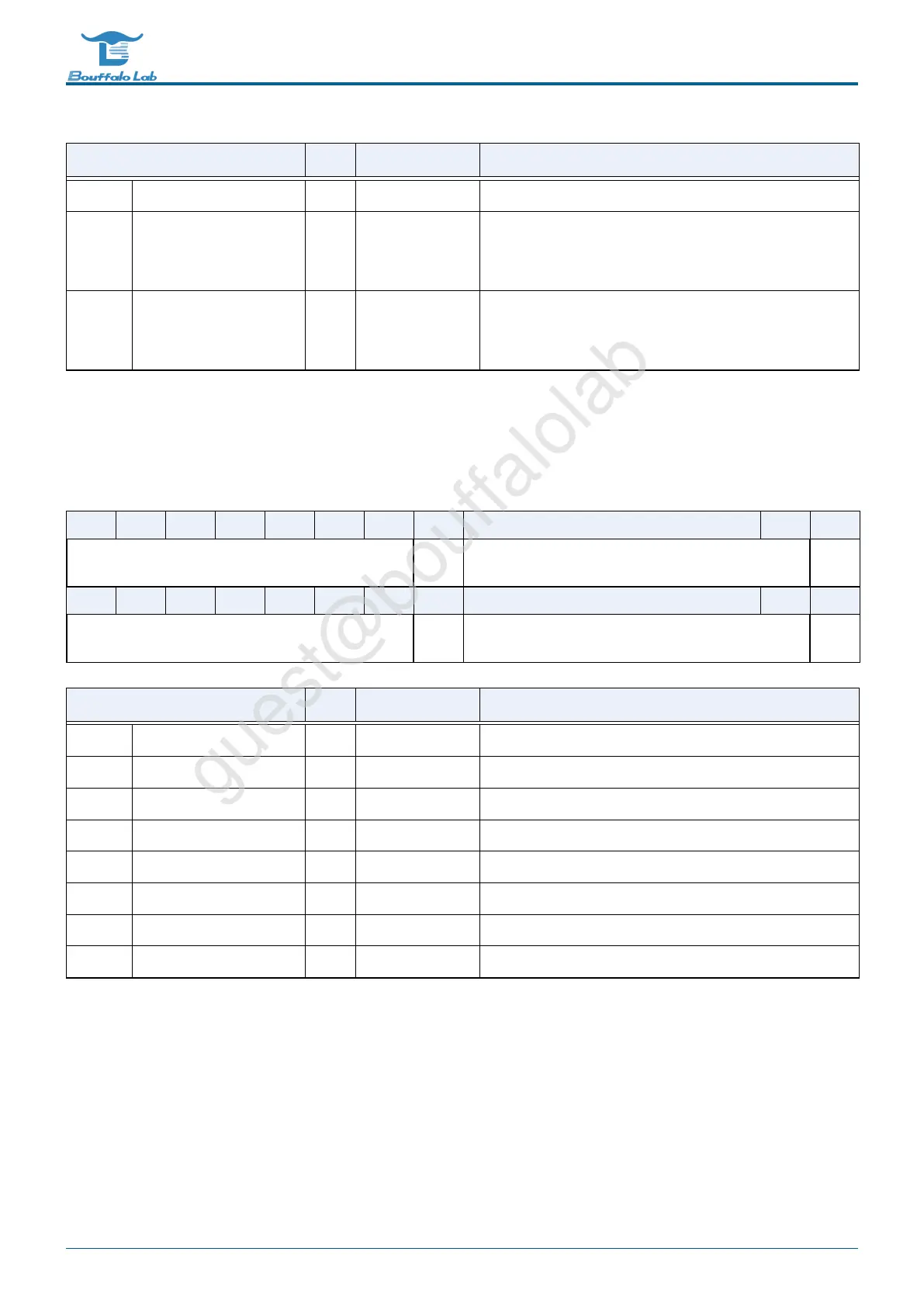

8.4.2 irtx_int_sts

Address:0x4000a604

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD TXE

EN

RSVD TXE

CLR

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD TXE

MASK

RSVD TXE

INT

Bits

Name Type Reset Description

31:25 RSVD

24 TXEEN R/W 1’b1 Interrupt enable of irtx_end_int

23:17 RSVD

16 TXECLR W1C 1’b0 Interrupt clear of irtx_end_int

15:9 RSVD

8 TXEMASK R/W 1’b1 Interrupt mask of irtx_end_int

7:1 RSVD

0 TXEINT R 1’b0 IRTX transfer end interrupt

BL702/704/706 Reference Manual 168/ 375

@2021 Bouffalo Lab

Loading...

Loading...