BL702/704/706 Reference Manual

Name

Description

irrx_data_word0 IR RX data word0

irrx_data_word1 IR RX data word1

irrx_swm_fifo_config_0 IR RX FIFO configuration

irrx_swm_fifo_rdata IR RX software mode pulse width data

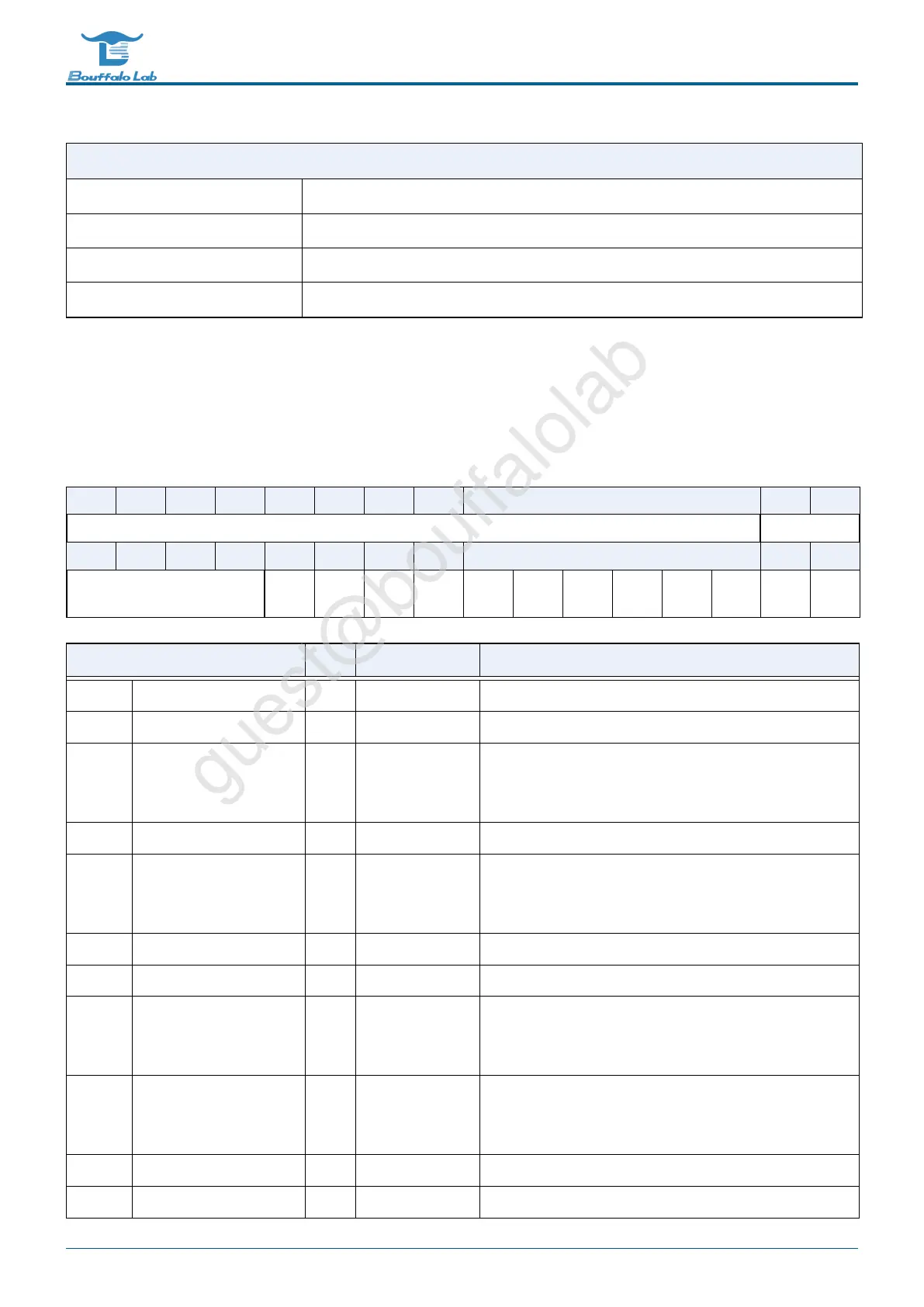

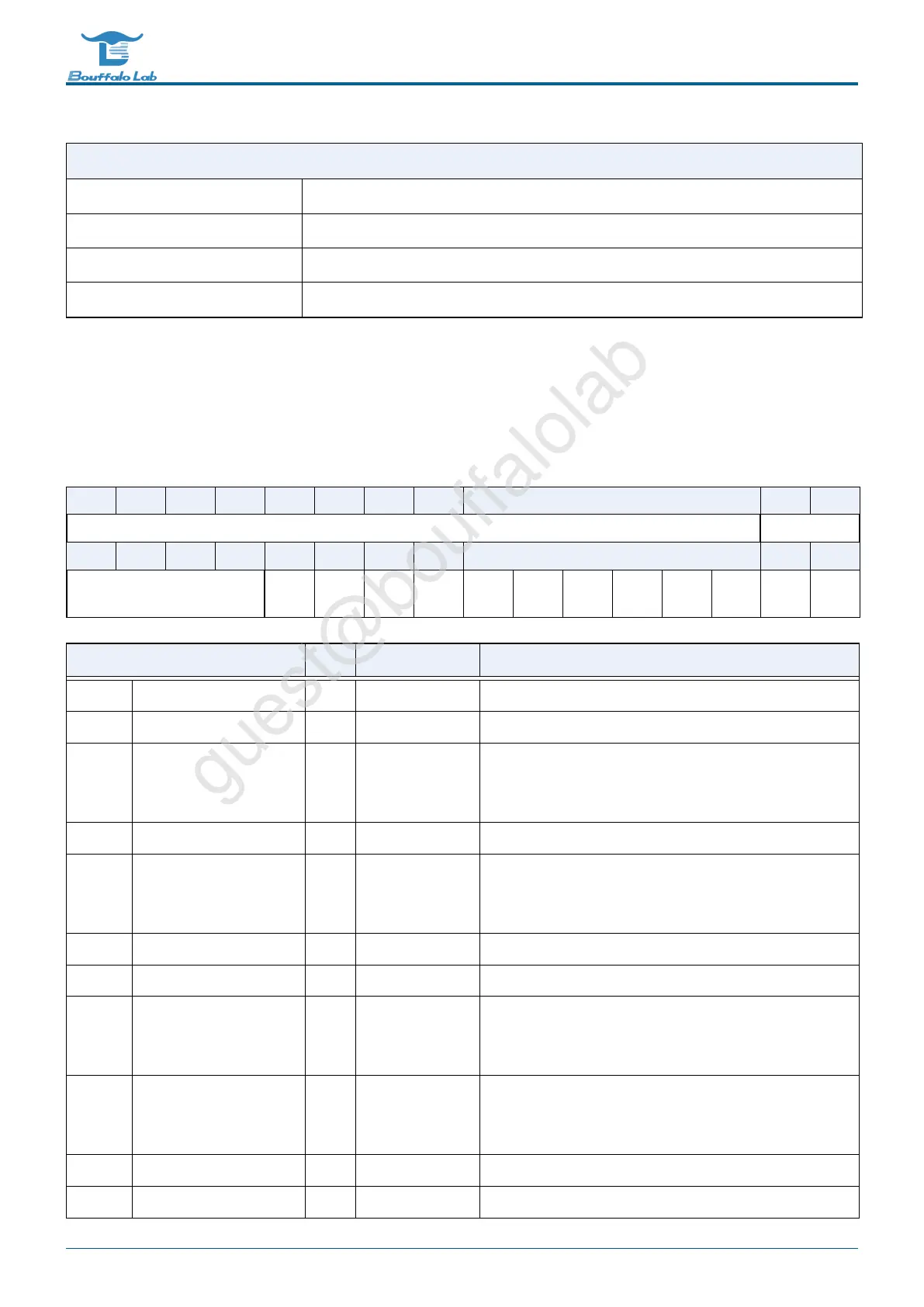

8.4.1 irtx_config

Address:0x4000a600

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD TXDATANU

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TXDATANU TPHL

IS

TXTP

EN

TXH

HLI

TXH

EN

RSVD TXL1

HLI

TXL0

HLI

TXDA

EN

TXSW

EN

TXMD

EN

TXO

EN

TXEN

Bits

Name Type Reset Description

31:18 RSVD

17:12 TXDATANU R/W 6’d31 Bit count of Data phase (unit: bit / PW for normal / SWM)

11 TPHLIS R/W 1’b0 Tail pulse H/L inverse signal (Don’t care if SWM is enabled)

0: Phase 0 is High (Active), phase 1 is Low (Idle) (H -> L)

1: Phase 0 is Low (Idle), phase 1 is High (Active) (L -> H)

10 TXTPEN R/W 1’b1 Enable signal of tail pulse (Don’t care if SWM is enabled)

9 TXHHLI R/W 1’b0 Tail pulse H/L inverse signal (Don’t care if SWM is enabled)

0: Phase 0 is High (Active), phase 1 is Low (Idle) (H -> L)

1: Phase 0 is Low (Idle), phase 1 is High (Active) (L -> H)

8 TXHEN R/W 1’b1 Enable signal of head pulse (Don’t care if SWM is enabled)

7 RSVD

6 TXL1HLI R/W 1’b0 Logic 1 H/L inverse signal (Don’t care if SWM is enabled)

0: Phase 0 is High (Active), phase 1 is Low (Idle) (H -> L)

1: Phase 0 is Low (Idle), phase 1 is High (Active) (L -> H)

5 TXL0HLI R/W 1’b0 Logic 0 H/L inverse signal (Don’t care if SWM is enabled)

0: Phase 0 is High (Active), phase 1 is Low (Idle) (H -> L)

1: Phase 0 is Low (Idle), phase 1 is High (Active) (L -> H)

4 TXDAEN R/W 1’b1 Enable signal of data phase (Don’t care if SWM is enabled)

3 TXSWEN R/W 1’b0 Enable signal of IRTX Software Mode (SWM)

BL702/704/706 Reference Manual 167/ 375

@2021 Bouffalo Lab

Loading...

Loading...