BL702/704/706 Reference Manual

8.3.5 Carrier modulation

Setting the upper 16 bits of the IRTX_PULSE_WIDTH register can generate carriers with different frequencies and

duty cycles. The <TXMPH1W> bit in this register sets the width of carrier phase 1, and the <TXMPH0W> bit sets the

width of carrier phase 0.

8.3.6 IR interrupt

IR has separate transmit and receive interrupts, and a transmit interrupt is generated when a transmit operation ends.

When a piece of data is received, it will wait for the continuous level to reach the set end threshold to generate a

receive interrupt.

The user can query the send interrupt status and clear the interrupt by register IRTX_INT_STS, and query the receive

interrupt status and clear the interrupt by register IRRX_INT_STS.

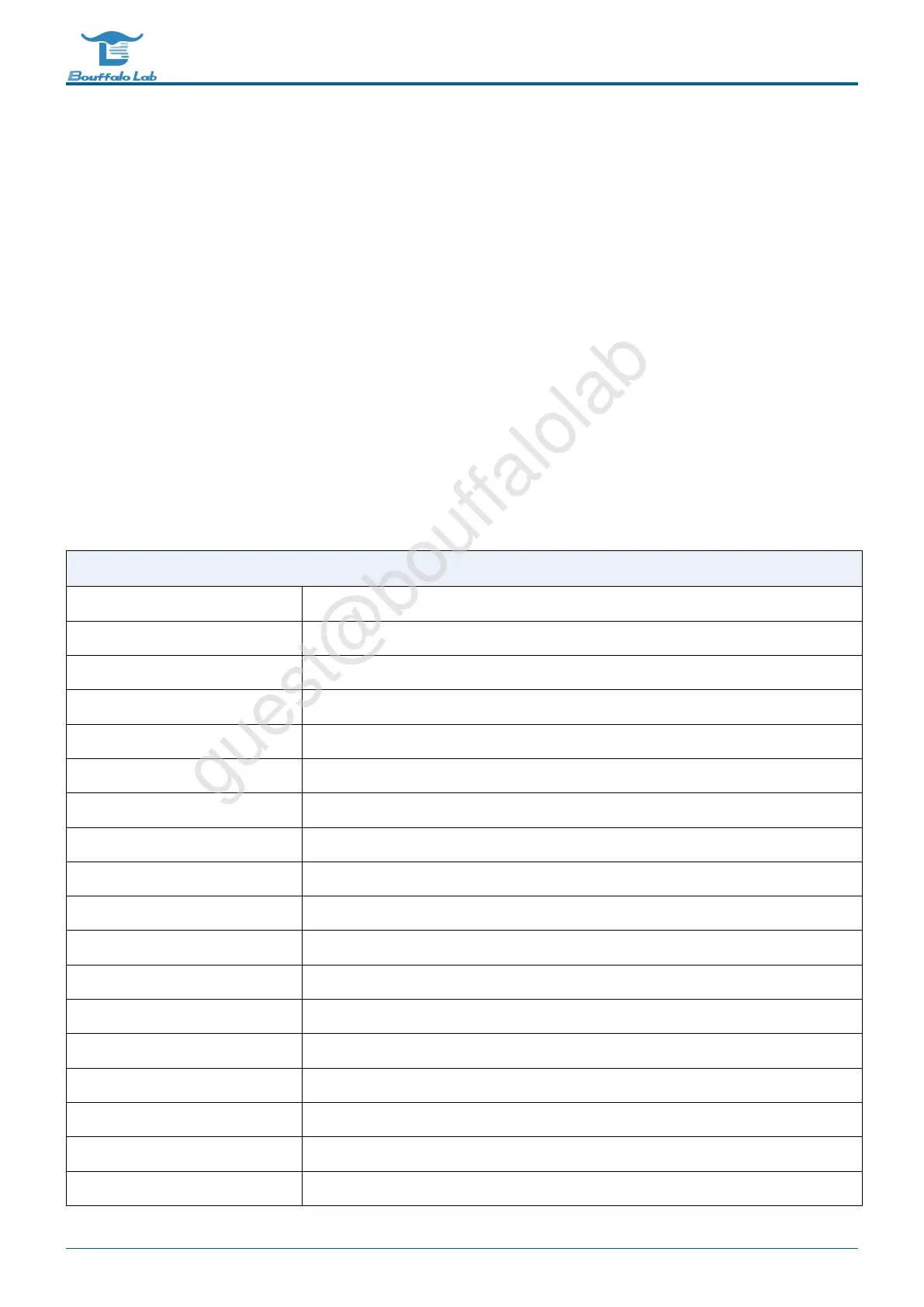

8.4 Register description

Name

Description

irtx_config IR TX configuration register

irtx_int_sts IR TX interrupt status

irtx_data_word0 IR TX data word0

irtx_data_word1 IR TX data word1

irtx_pulse_width IR TX pulse width

irtx_pw IR TX pulse width of phase

irtx_swm_pw_0 IR TX Software Mode pulse width data0

irtx_swm_pw_1 IR TX Software Mode pulse width data1

irtx_swm_pw_2 IR TX Software Mode pulse width data2

irtx_swm_pw_3 IR TX Software Mode pulse width data3

irtx_swm_pw_4 IR TX Software Mode pulse width data4

irtx_swm_pw_5 IR TX Software Mode pulse width data5

irtx_swm_pw_6 IR TX Software Mode pulse width data6

irtx_swm_pw_7 IR TX Software Mode pulse width data7

irrx_config IR RX configuration register

irrx_int_sts IR RX interrupt status

irrx_pw_config IR RX pulse width configuration

irrx_data_count IR RX data bit count

BL702/704/706 Reference Manual 166/ 375

@2021 Bouffalo Lab

Loading...

Loading...