BL702/704/706 Reference Manual

Bits

Name Type Reset Description

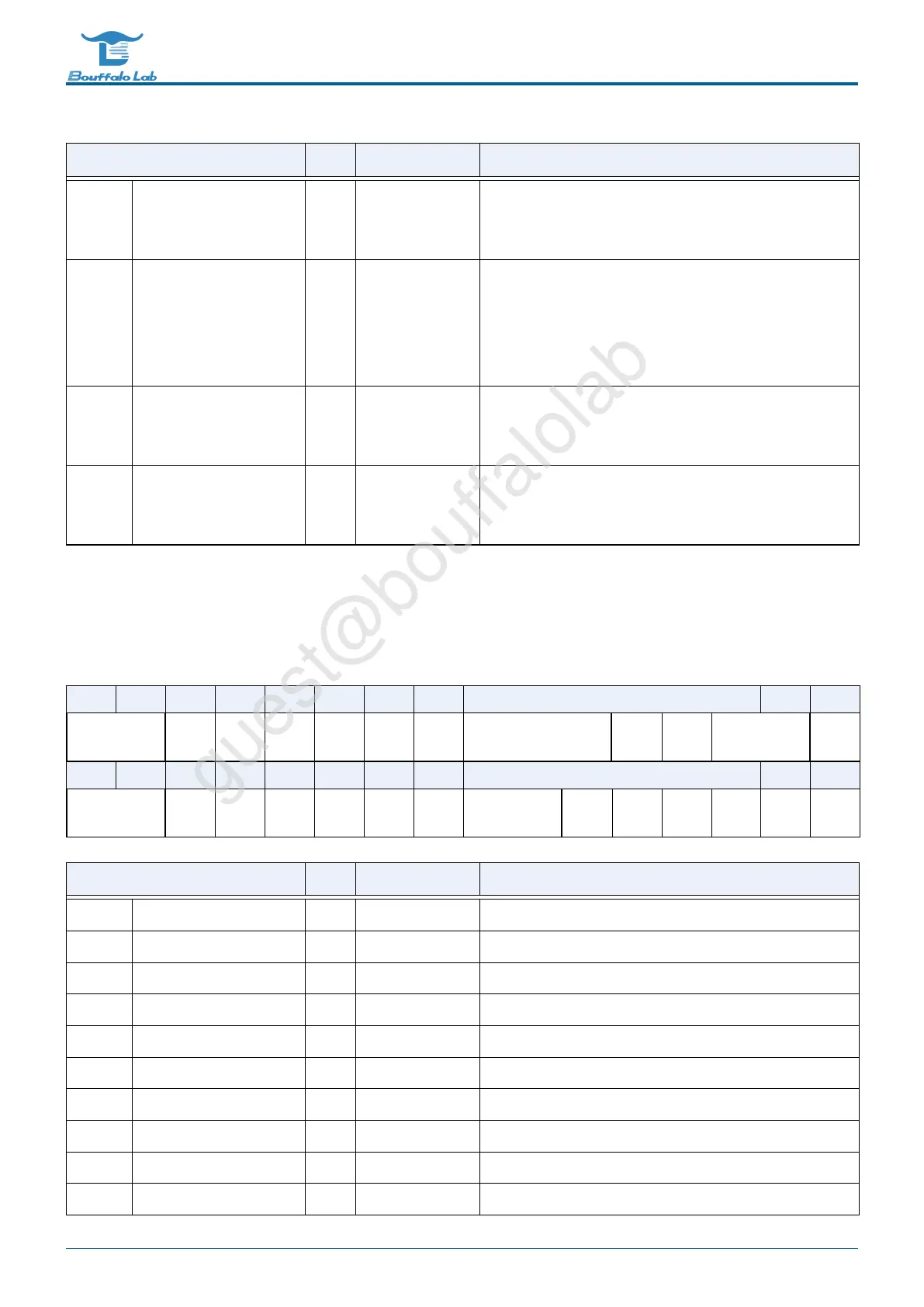

4 SCLKPOL R/W 1’b0 SCLK polarity

0: SCLK output LOW at IDLE state

1: SCLK output HIGH at IDLE state

3:2 FSIZE R/W 2’d0 SPI frame size (also the valid width for each FIFO entry)

2’d0: 8-bit

2’d1: 16-bit

2’d2: 24-bit

2’d3: 32-bit

1 SEN R/W 1’b0 Enable signal of SPI Slave function, Master and Slave

should not be both enabled at the same time

(This bit becomes don’t-care if cr_spi_m_en is enabled)

0 MEN R/W 1’b0 Enable signal of SPI Master function

Asserting this bit will trigger the transaction, and should be

de-asserted after finish

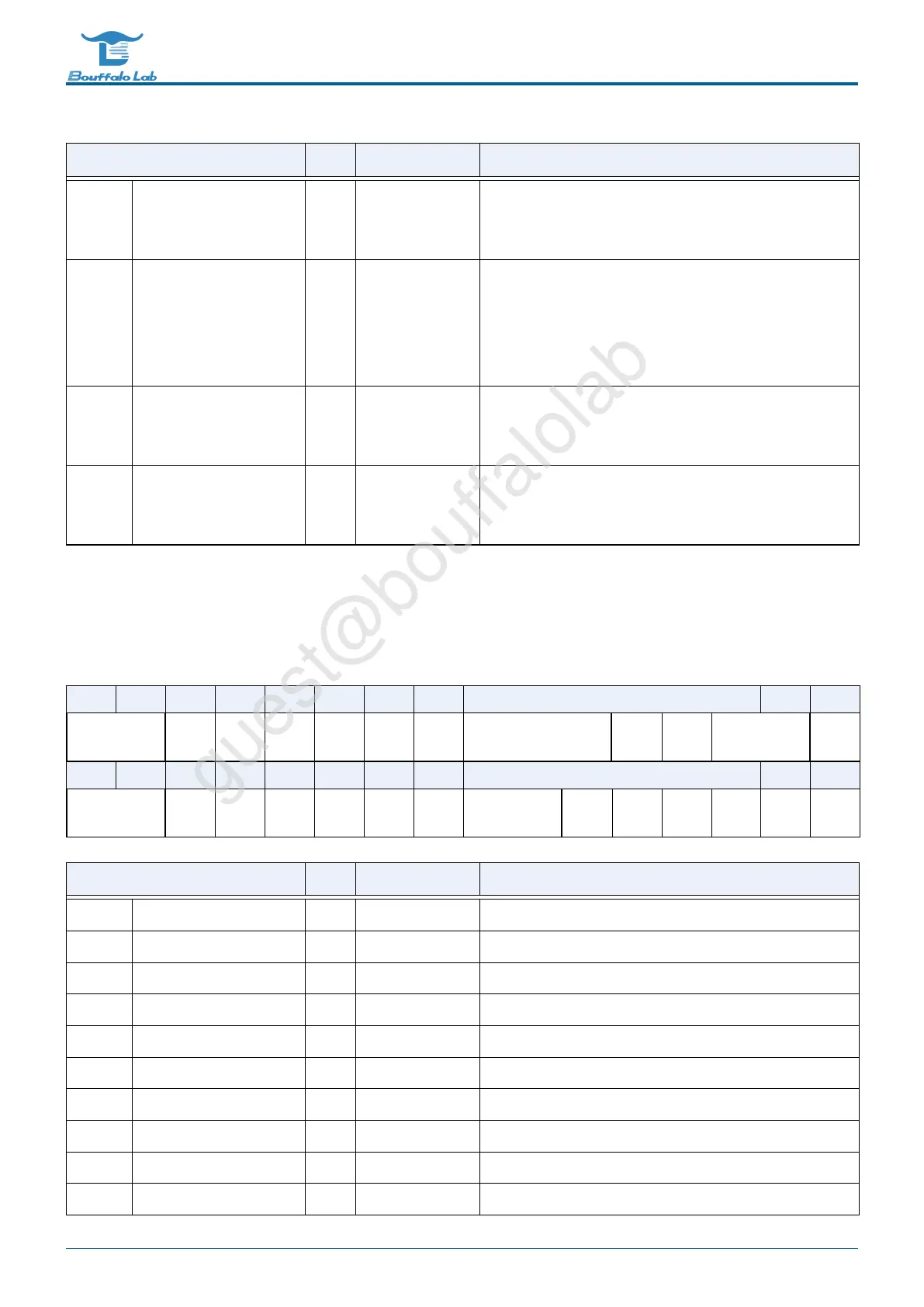

9.4.2 spi_int_sts

Address:0x4000a204

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD FER

EN

TXU

EN

STO

EN

RXF

EN

TXF

EN

END

EN

RSVD TXU

CLR

STO

CLR

RSVD END

CLR

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD FER

MASK

TXU

MASK

STO

MASK

RXF

MASK

TXF

MASK

END

MASK

RSVD FER

INT

TXU

INT

STO

INT

RXF

INT

TXF

INT

END

INT

Bits

Name Type Reset Description

31:30 RSVD

29 FEREN R/W 1’b1 Interrupt enable of spi_fer_int

28 TXUEN R/W 1’b1 Interrupt enable of spi_txu_int

27 STOEN R/W 1’b1 Interrupt enable of spi_sto_int

26 RXFEN R/W 1’b1 Interrupt enable of spi_rxv_int

25 TXFEN R/W 1’b1 Interrupt enable of spi_txe_int

24 ENDEN R/W 1’b1 Interrupt enable of spi_end_int

23:21 RSVD

20 TXUCLR W1C 1’b0 Interrupt clear of spi_txu_int

19 STOCLR W1C 1’b0 Interrupt clear of spi_sto_int

BL702/704/706 Reference Manual 183/ 375

@2021 Bouffalo Lab

Loading...

Loading...