BL702/704/706 Reference Manual

Bits

Name Type Reset Description

31:1 RSVD

0 BUSBUSY R 1’b0 Indicator of SPI bus busy

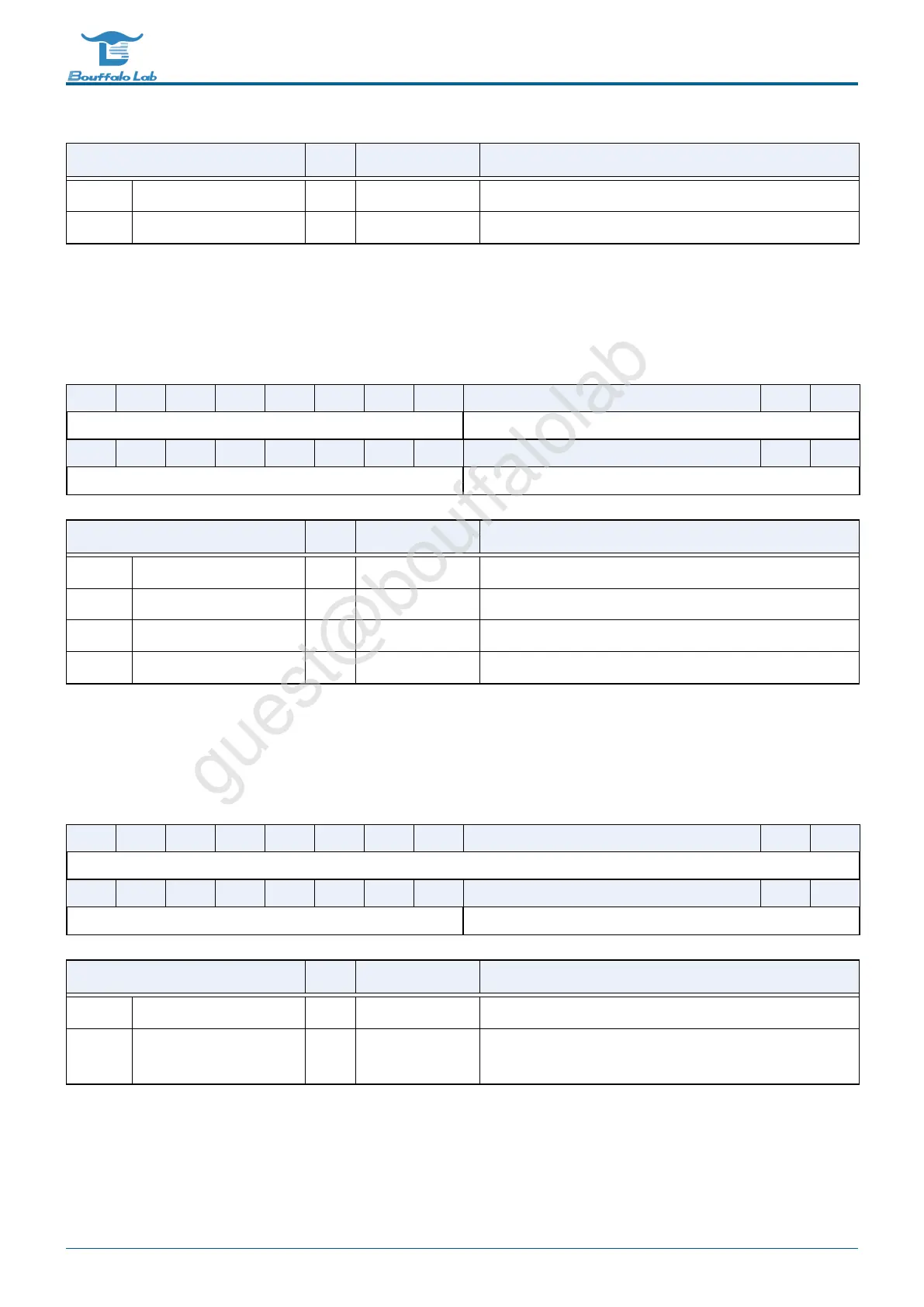

9.4.4 spi_prd_0

Address:0x4000a210

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PRDPH1 PRDPH0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

PRDP PRDS

Bits

Name Type Reset Description

31:24 PRDPH1 R/W 8’d15 Length of DATA phase 1 (please refer to ”Timing” tab)

23:16 PRDPH0 R/W 8’d15 Length of DATA phase 0 (please refer to ”Timing” tab)

15:8 PRDP R/W 8’d15 Length of STOP condition (please refer to ”Timing” tab)

7:0 PRDS R/W 8’d15 Length of START condition (please refer to ”Timing” tab)

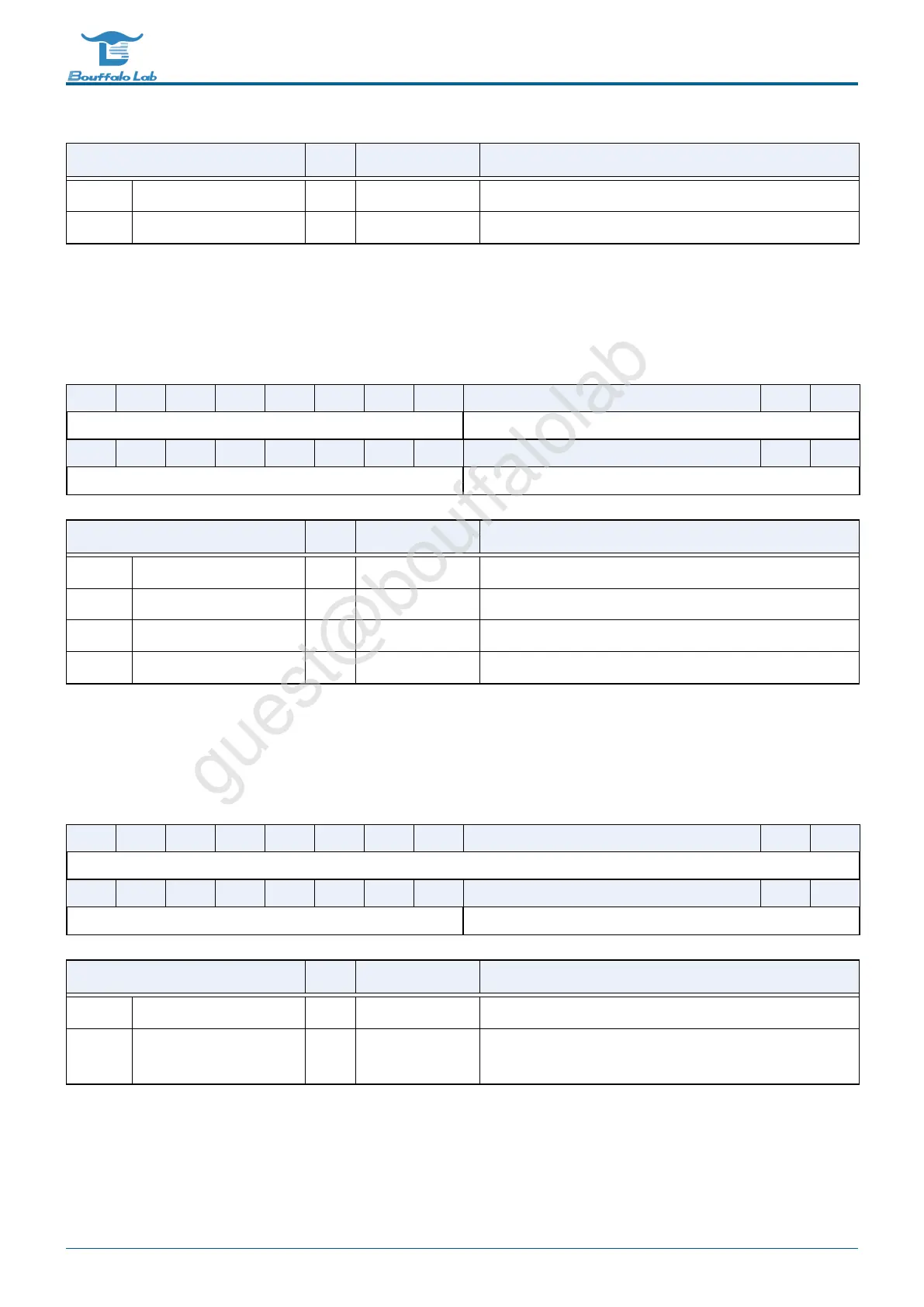

9.4.5 spi_prd_1

Address

:

0x4000a214

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD PRDI

Bits

Name Type Reset Description

31:8 RSVD

7:0 PRDI R/W 8’d15 Length of INTERVAL between frame (please refer to ”Tim-

ing” tab)

BL702/704/706 Reference Manual 185/ 375

@2021 Bouffalo Lab

Loading...

Loading...