BL702/704/706 Reference Manual

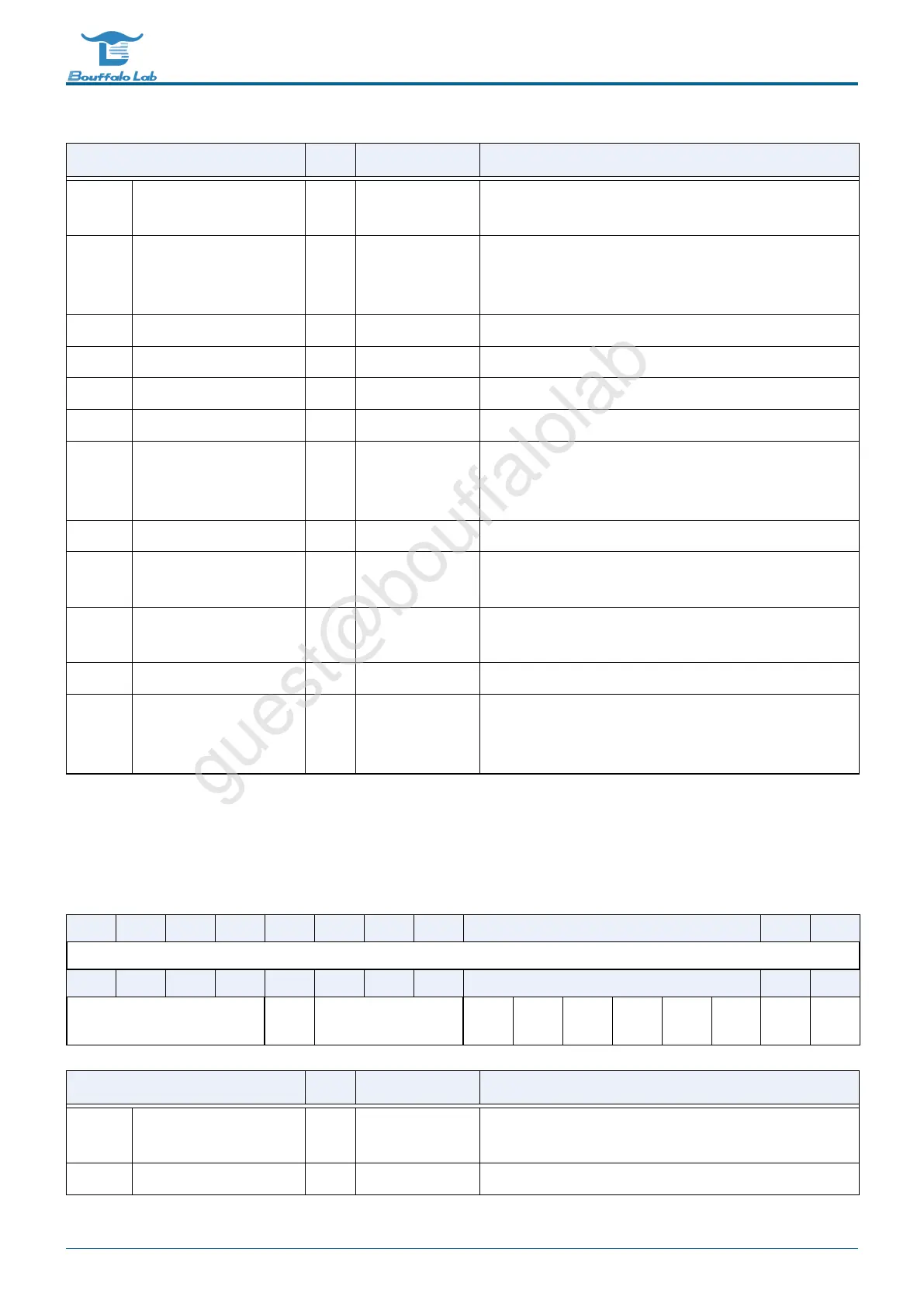

Bits

Name Type Reset Description

31:16 TXLEN R/W 16’d0 Length of UART TX data transfer (Unit: character/byte)

(Don’t-care if cr_utx_frm_en is enabled)

15:13 TXBCNTP R/W 3’d4 UART TX BREAK bit count (for LIN protocol)

Note: Additional 8 bit times will be added since LIN Break

field requires at least 13 bit times

12:11 TXBCNTP R/W 2’d1 UART TX STOP bit count (unit: 0.5 bit)

10:8 TXBCNTD R/W 3’d7 UART TX DATA bit count for each character

7 IRTXINV R/W 1’b0 Inverse signal of UART TX output in IR mode

6 IRTXEN R/W 1’b0 Enable signal of UART TX IR mode

5 TXPRSEL R/W 1’b0 Select signal of UART TX parity bit

1: Odd parity

0: Even parity

4 TXPREN R/W 1’b0 Enable signal of UART TX parity bit

3 TLINEN R/W 1’b0 Enable signal of UART TX LIN mode (LIN header will be

sent before sending data)

2 FRMEN R/W 1’b0 Enable signal of UART TX freerun mode (utx_end_int will

be disabled)

1 CTSEN R/W 1’b0 Enable signal of UART TX CTS flow control function

0 EN R/W 1’b0 Enable signal of UART TX function

Asserting this bit will trigger the transaction, and should be

de-asserted after finish

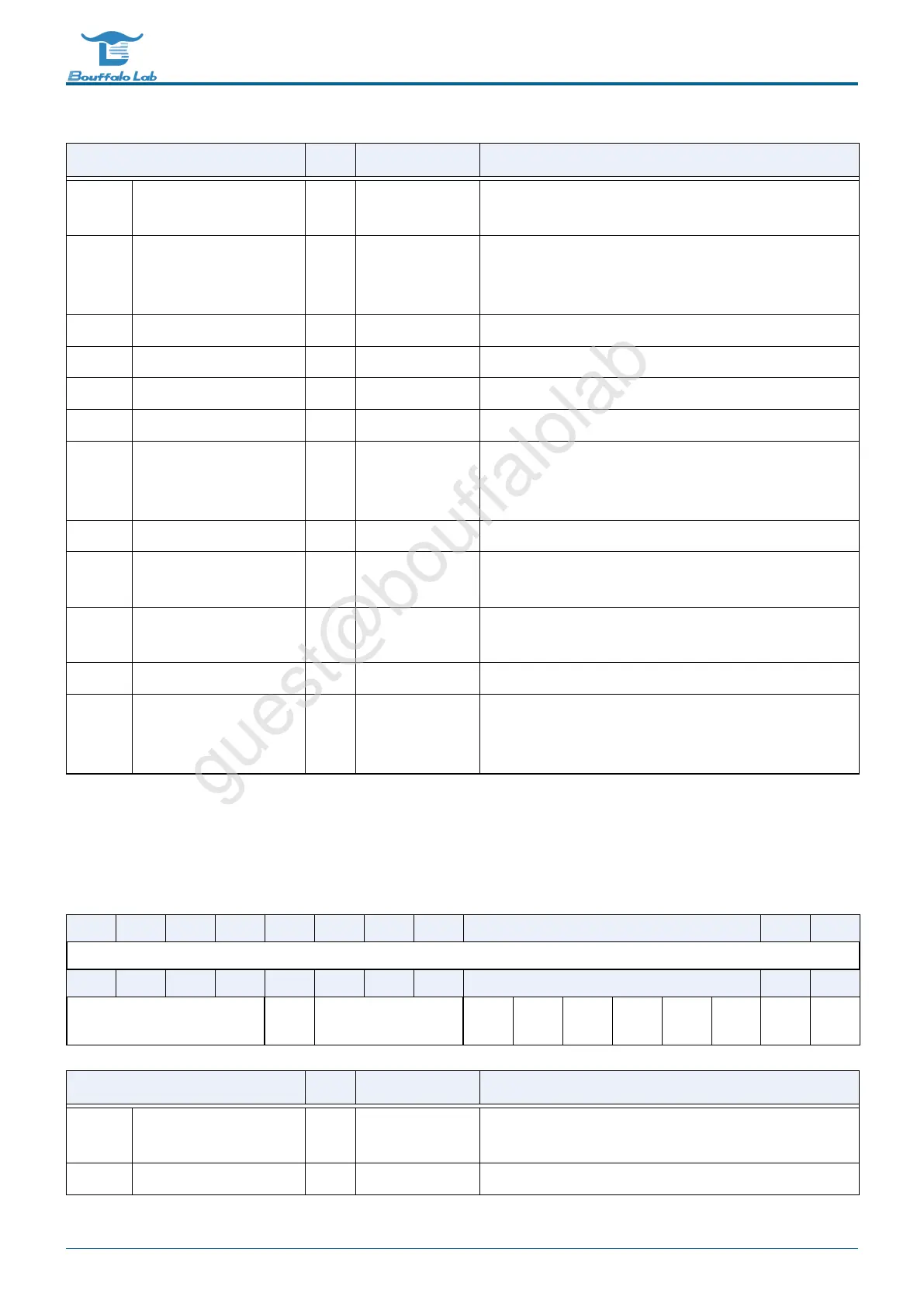

10.4.2 urx_config

Address:0x4000a004

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RXLEN

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DEGCNT DEG

EN

RXBCNTD IRRX

INV

IRRX

EN

RXPR

SEL

RXPR

EN

RLIN

EN

RSVD ABR

EN

EN

Bits

Name Type Reset Description

31:16 RXLEN R/W 16’d0 Length of UART RX data transfer (Unit: character/byte)

urx_end_int will assert when this length is reached

15:12 DEGCNT R/W 4’d0 De-glitch function cycle count

BL702/704/706 Reference Manual 197/ 375

@2021 Bouffalo Lab

Loading...

Loading...