BL702/704/706 Reference Manual

10.4 Register description

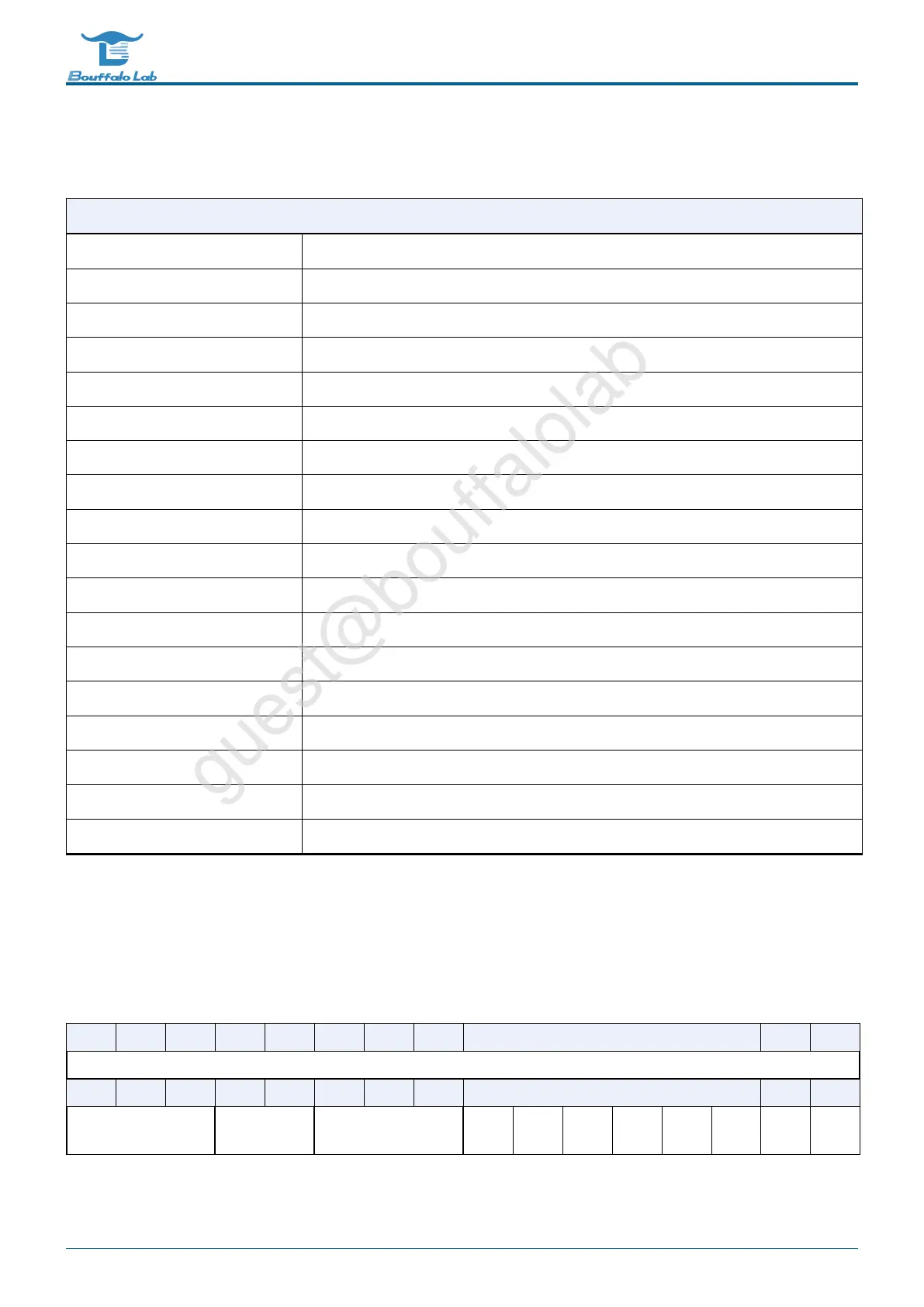

Name

Description

utx_config UART TX configuration register

urx_config UART RX configuration register

uart_bit_prd UART period control register

data_config UART data configuration register

utx_ir_position UART TX ir position control register

urx_ir_position UART RX ir position control register

urx_rto_timer RTO interrupt control register

uart_sw_mode UART SW mode configuration register

uart_int_sts UART interrupt status

uart_int_mask UART interrupt mask

uart_int_clear UART interrupt clear

uart_int_en UART interrupt enable

uart_status UART status control register

sts_urx_abr_prd Auto baud detection control register

uart_fifo_config_0 UART FIFO configuration register0

uart_fifo_config_1 UART FIFO configuration register1

uart_fifo_wdata UART FIFO write data

uart_fifo_rdata UART FIFO read data

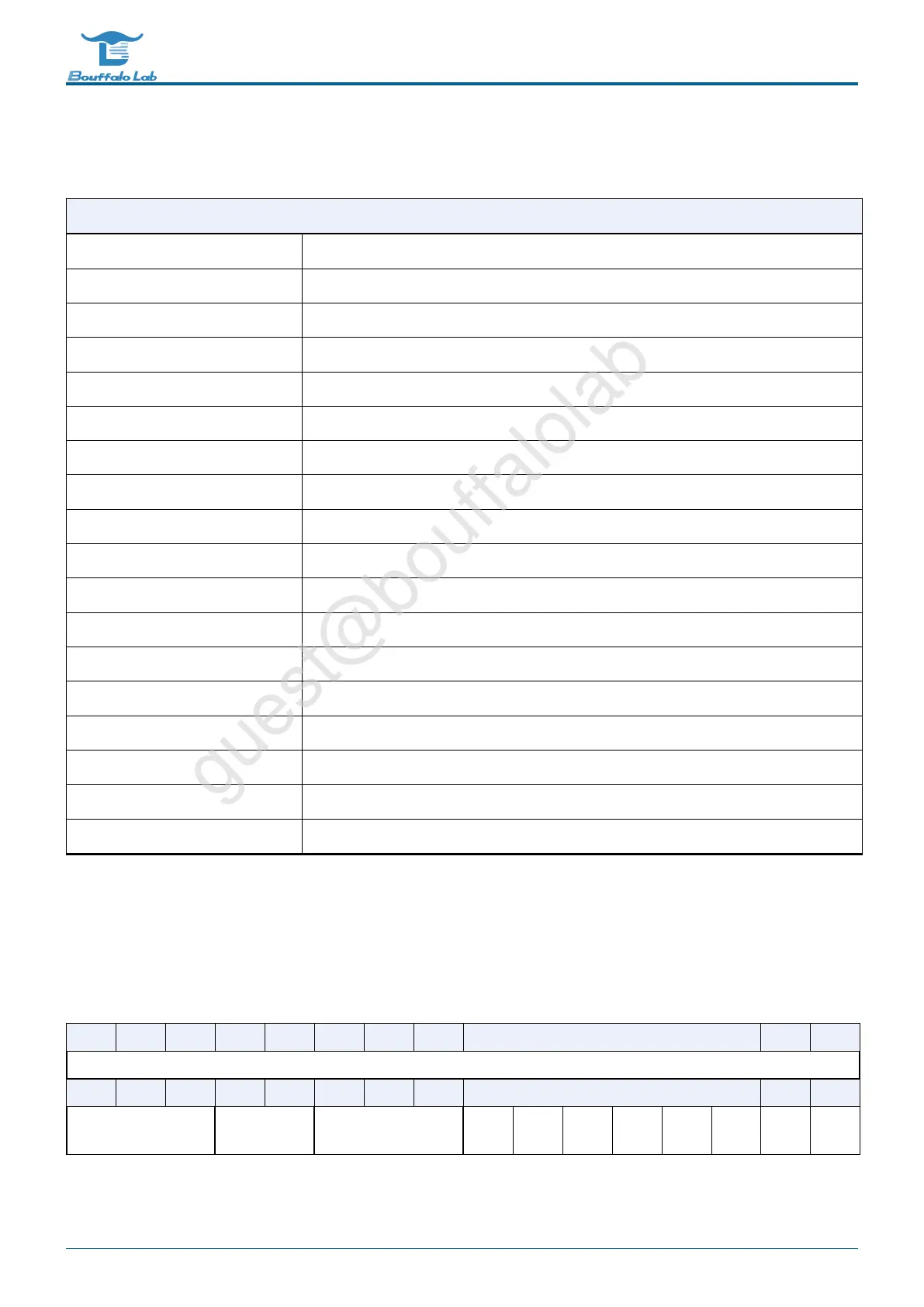

10.4.1 utx_config

Address:0x4000a000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TXLEN

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TXBCNTP TXBCNTP TXBCNTD IRTX

INV

IRTX

EN

TXPR

SEL

TXPR

EN

TLIN

EN

FRM

EN

CTS

EN

EN

BL702/704/706 Reference Manual 196/ 375

@2021 Bouffalo Lab

Loading...

Loading...