BL702/704/706 Reference Manual

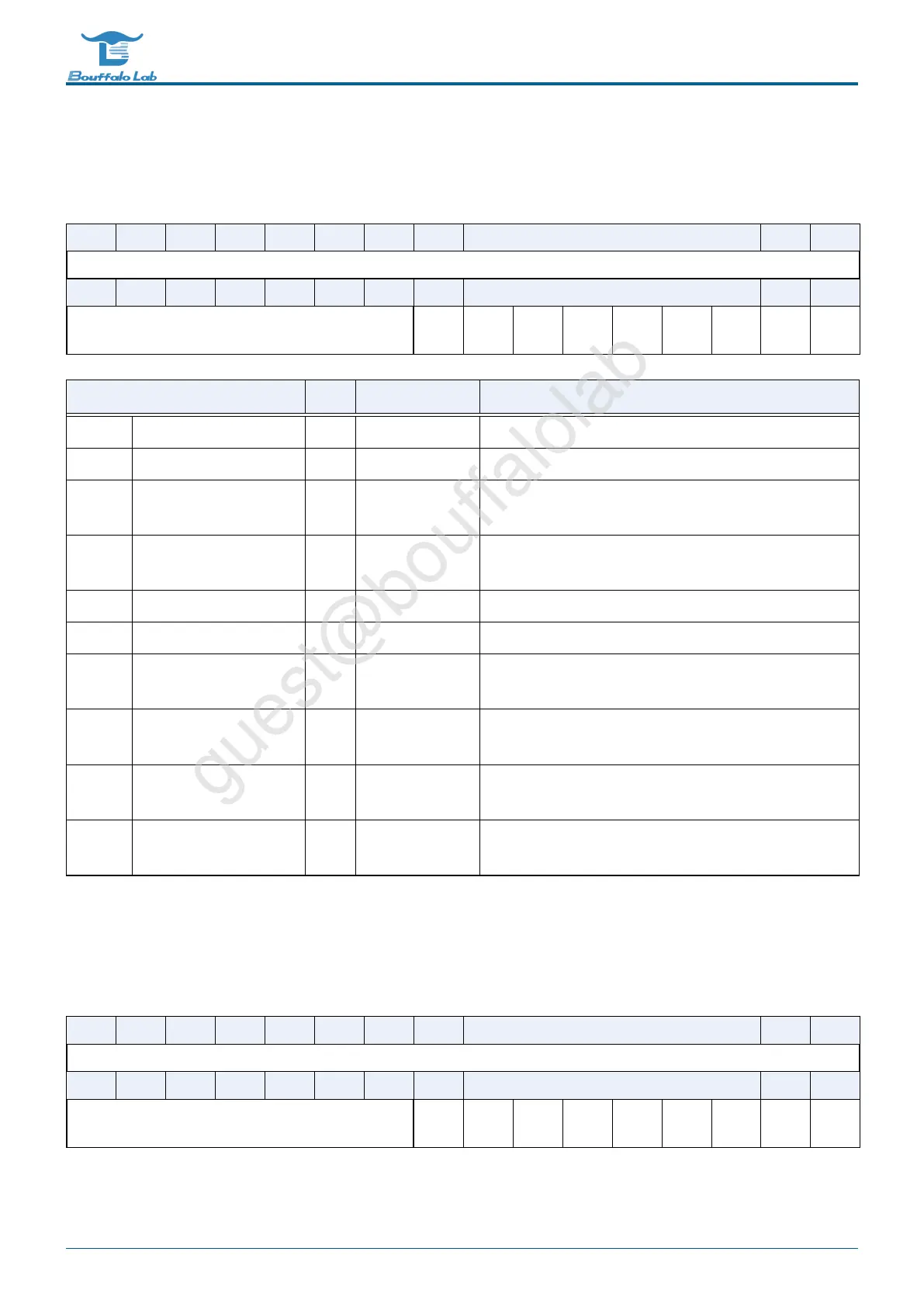

10.4.9 uart_int_sts

Address:0x4000a020

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RLSE

INT

RFER

INT

TFIN RPCE

INT

RRTO

INT

RFIN TFIN REIN TEIN

Bits

Name Type Reset Description

31:9 RSVD

8 RLSEINT R 1’b0 UART RX LIN mode sync field error interrupt

7 RFERINT R 1’b0 UART RX FIFO error interrupt, auto-cleared when FIFO

overflow/underflow error flag is cleared

6 TFIN R 1’b0 UART TX FIFO error interrupt, auto-cleared when FIFO

overflow/underflow error flag is cleared

5 RPCEINT R 1’b0 UART RX parity check error interrupt

4 RRTOINT R 1’b0 UART RX Time-out interrupt

3 RFIN R 1’b0 UART RX FIFO ready (rx_fifo_cnt > rx_fifo_th) interrupt,

auto-cleared when data is popped

2 TFIN R 1’b0 UART TX FIFO ready (tx_fifo_cnt > tx_fifo_th) interrupt,

auto-cleared when data is pushed

1 REIN R 1’b0 UART RX transfer end interrupt (set according to cr_urx_-

len)

0 TEIN R 1’b0 UART TX transfer end interrupt (set according to cr_utx_-

len)

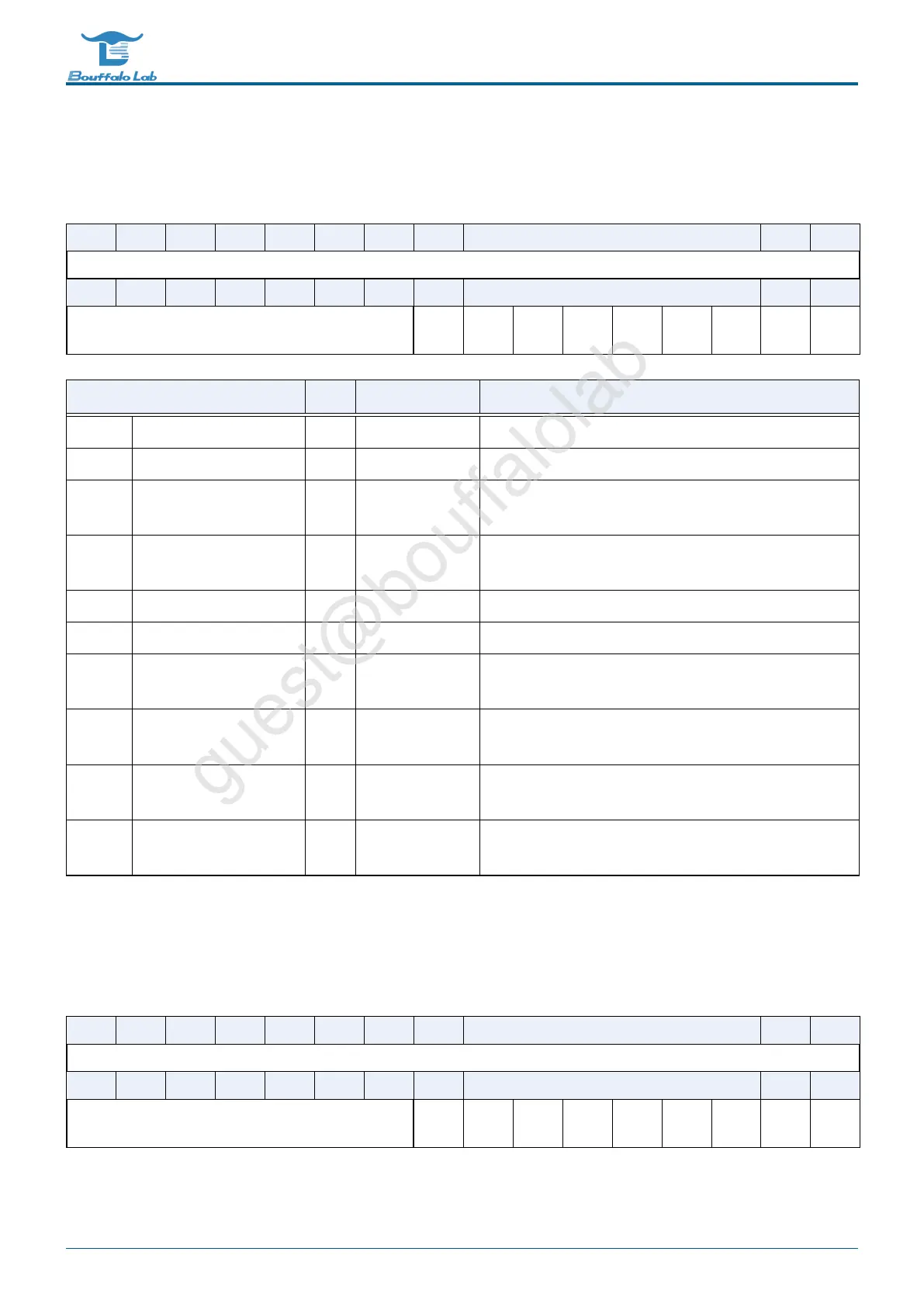

10.4.10 uart_int_mask

Address:0x4000a024

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RLSE

MASK

RFER

MASK

TFER

MASK

RPCE

MASK

RRTO

MASK

RFMS TFMS REMS TEMS

BL702/704/706 Reference Manual 201/ 375

@2021 Bouffalo Lab

Loading...

Loading...