BL702/704/706 Reference Manual

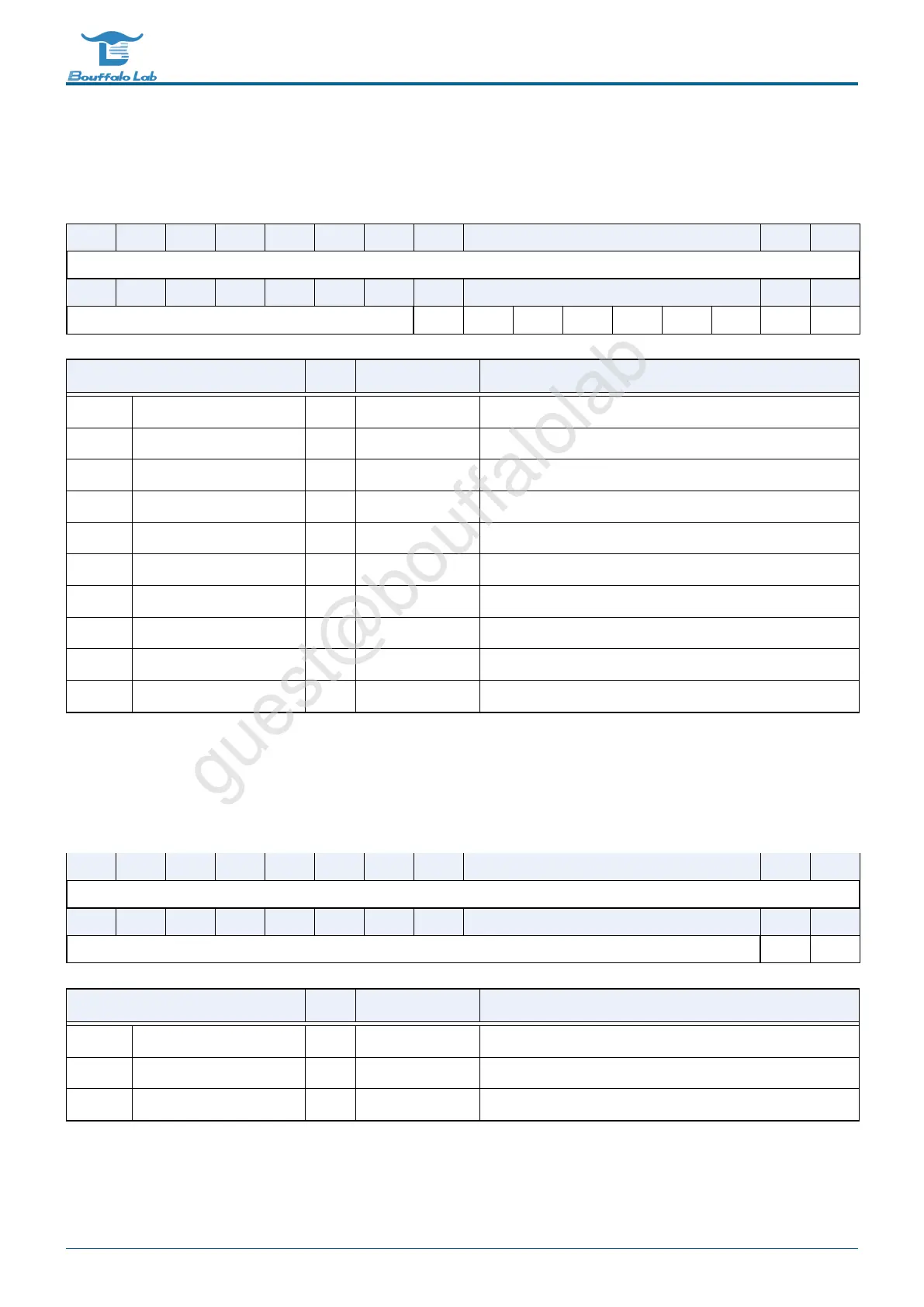

10.4.12 uart_int_en

Address:0x4000a02c

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RLSE RFER TFER RPCE RRTO RFIF TFIF REND TEND

Bits

Name Type Reset Description

31:9 RSVD

8 RLSE R/W 1’b1 Interrupt enable of urx_lse_int

7 RFER R/W 1’b1 Interrupt enable of urx_fer_int

6 TFER R/W 1’b1 Interrupt enable of utx_fer_int

5 RPCE R/W 1’b1 Interrupt enable of urx_pce_int

4 RRTO R/W 1’b1 Interrupt enable of urx_rto_int

3 RFIF R/W 1’b1 Interrupt enable of urx_fifo_int

2 TFIF R/W 1’b1 Interrupt enable of utx_fifo_int

1 REND R/W 1’b1 Interrupt enable of urx_end_int

0 TEND R/W 1’b1 Interrupt enable of utx_end_int

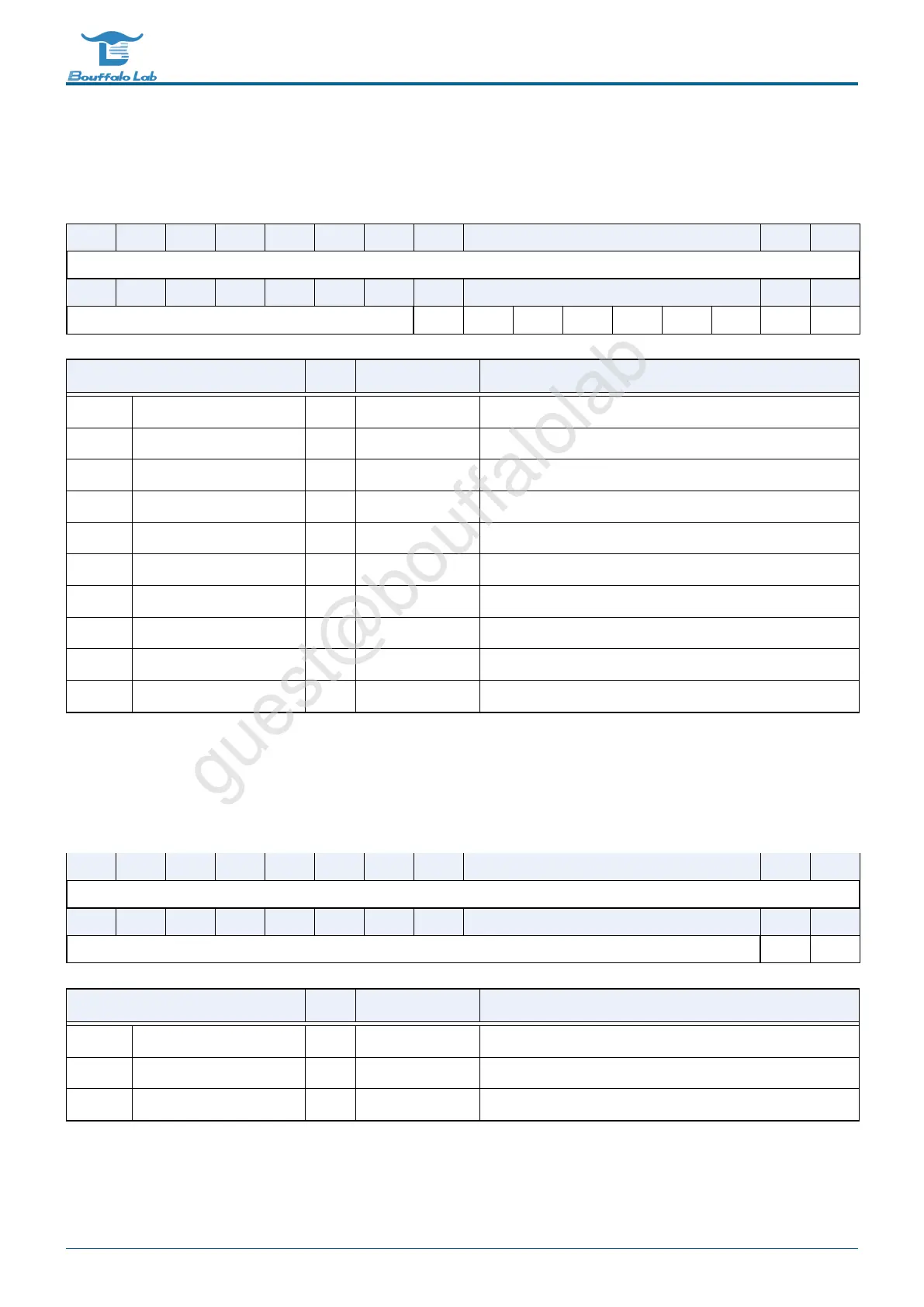

10.4.13 uart_status

Address:0x4000a030

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RBB TBB

Bits

Name Type Reset Description

31:2 RSVD

1 RBB R 1’b0 Indicator of UART RX bus busy

0 TBB R 1’b0 Indicator of UART TX bus busy

BL702/704/706 Reference Manual 203/ 375

@2021 Bouffalo Lab

Loading...

Loading...