BL702/704/706 Reference Manual

Name

Description

i2c_bus_busy I2C bus busy control register

i2c_prd_start I2C length of start phase

i2c_prd_stop I2C length of stop phase

i2c_prd_data I2C length of data phase

i2c_fifo_config_0 I2C FIFO configuration register0

i2c_fifo_config_1 I2C FIFO configuration register1

i2c_fifo_wdata I2C FIFO write data

i2c_fifo_rdata I2C FIFO read data

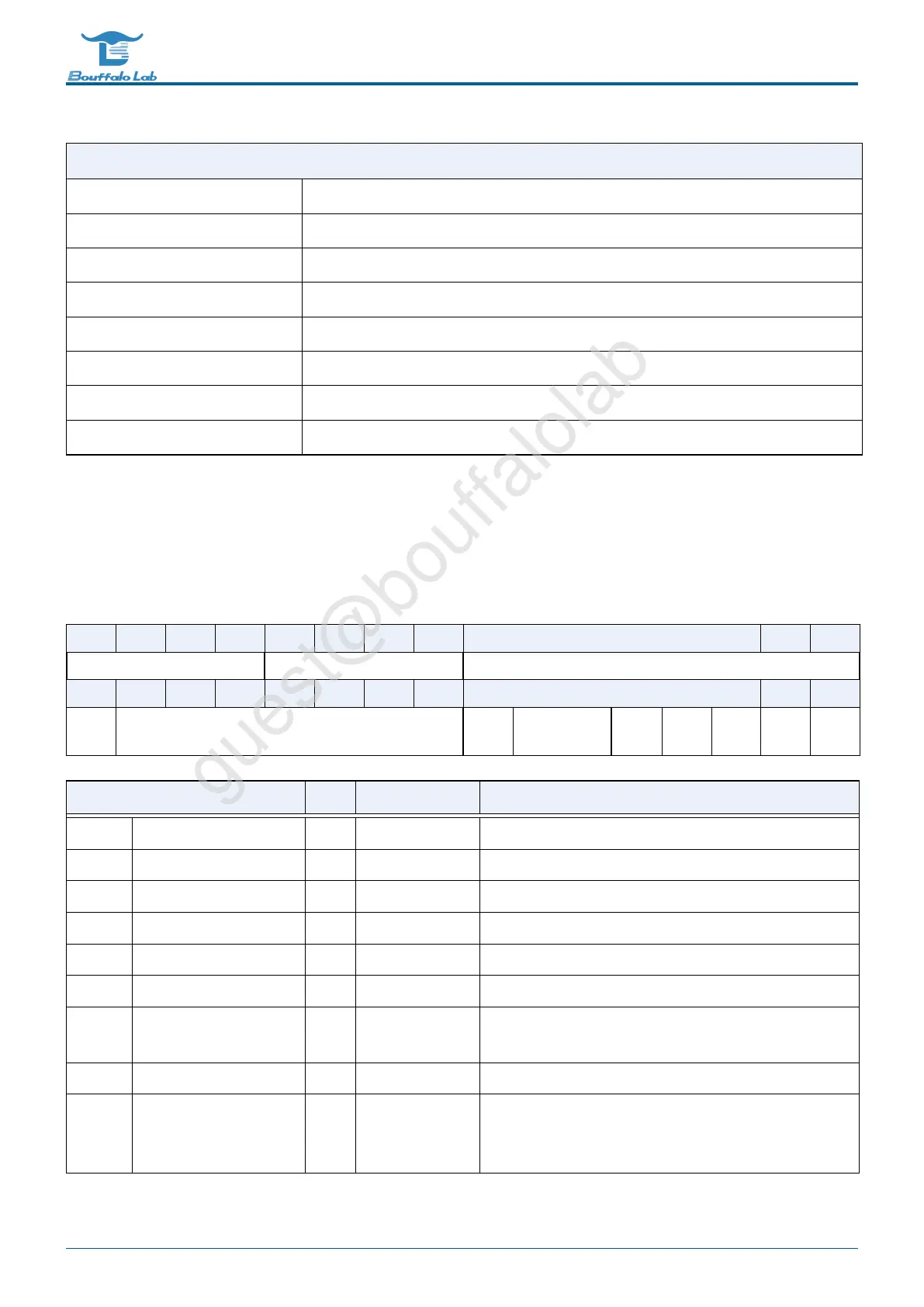

11.9.1 i2c_config

Address:0x4000a300

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DEGCNT RSVD PKTLEN

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD SLVADDR RSVD SABC SAEN SCLS

EN

DEG

EN

PKT

DIR

MEN

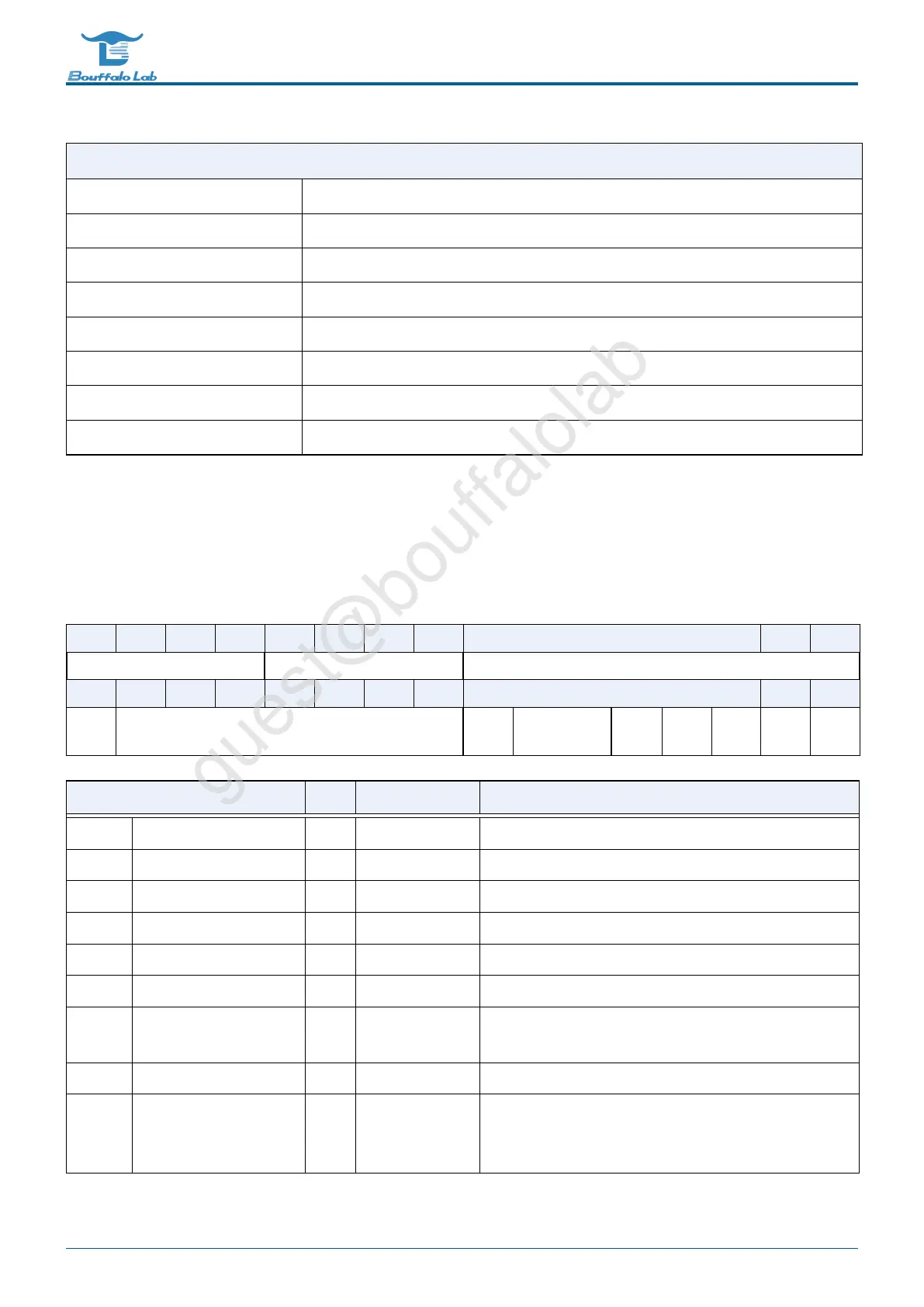

Bits

Name Type Reset Description

31:28 DEGCNT R/W 4’d0 De-glitch function cycle count

27:24 RSVD

23:16 PKTLEN R/W 8’d0 Packet length (unit: byte)

15 RSVD

14:8 SLVADDR R/W 7’d0 Slave address for I2C transaction (target address)

7 RSVD

6:5 SABC R/W 2’d0 Sub-address field byte count

2’d0: 1-byte, 2’d1: 2-byte, 2’d2: 3-byte, 2’d3: 4-byte

4 SAEN R/W 1’b0 Enable signal of I2C sub-address field

3 SCLSEN R/W 1’b1 Enable signal of I2C SCL synchronization, should be en-

abled to support Multi-Master and Clock-Stretching

(Normally should not be turned-off)

BL702/704/706 Reference Manual 215/ 375

@2021 Bouffalo Lab

Loading...

Loading...