BL702/704/706 Reference Manual

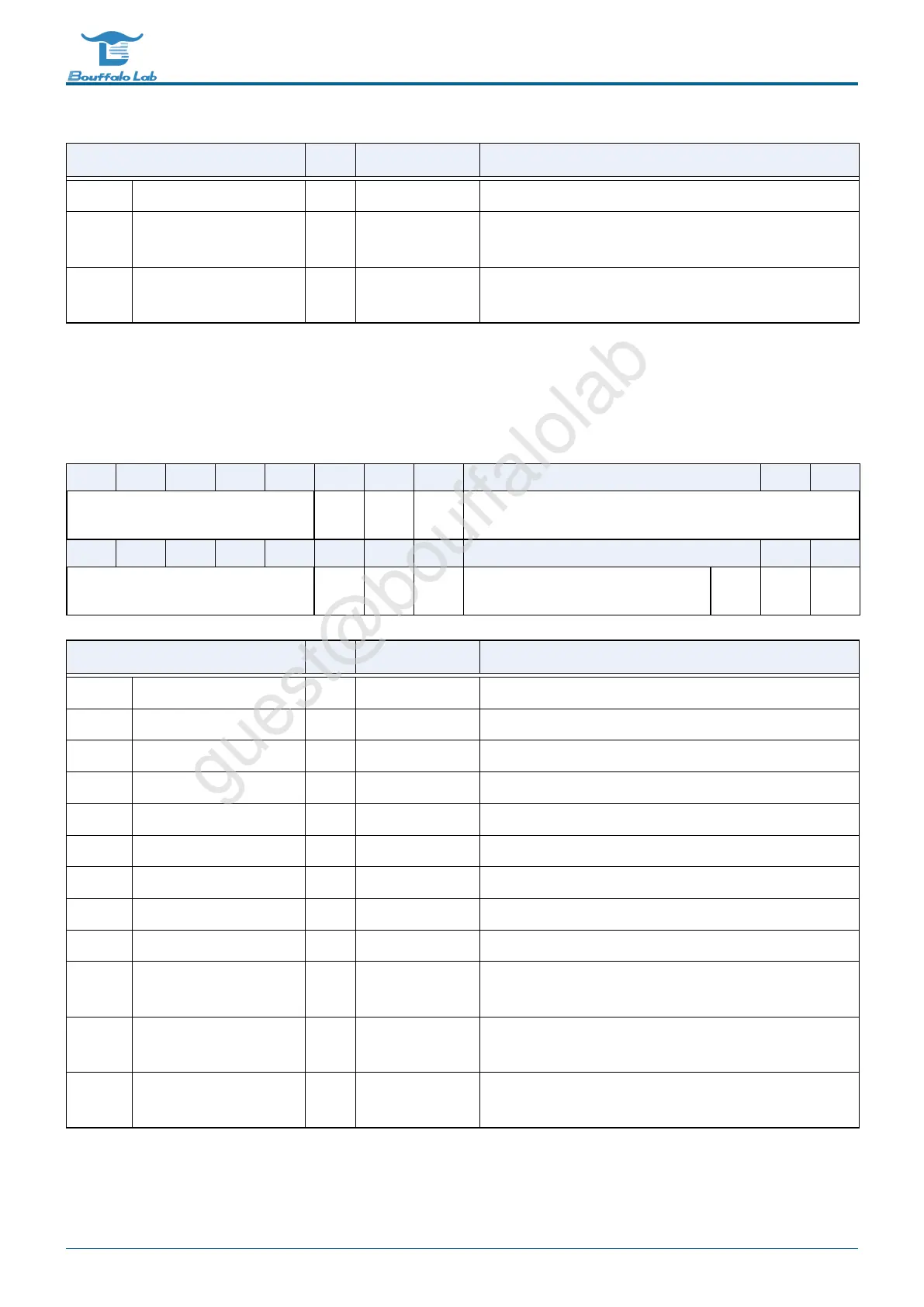

Bits

Name Type Reset Description

2 TXDEN R/W 1’b0 Enable signal of I2S TXD signal

1 SLAEN R/W 1’b0 Enable signal of I2S Slave function, cannot enable both

csr_i2s_m_en & csr_i2s_s_en

0 MASEN R/W 1’b0 Enable signal of I2S Master function, cannot enable both

csr_i2s_m_en & csr_i2s_s_en

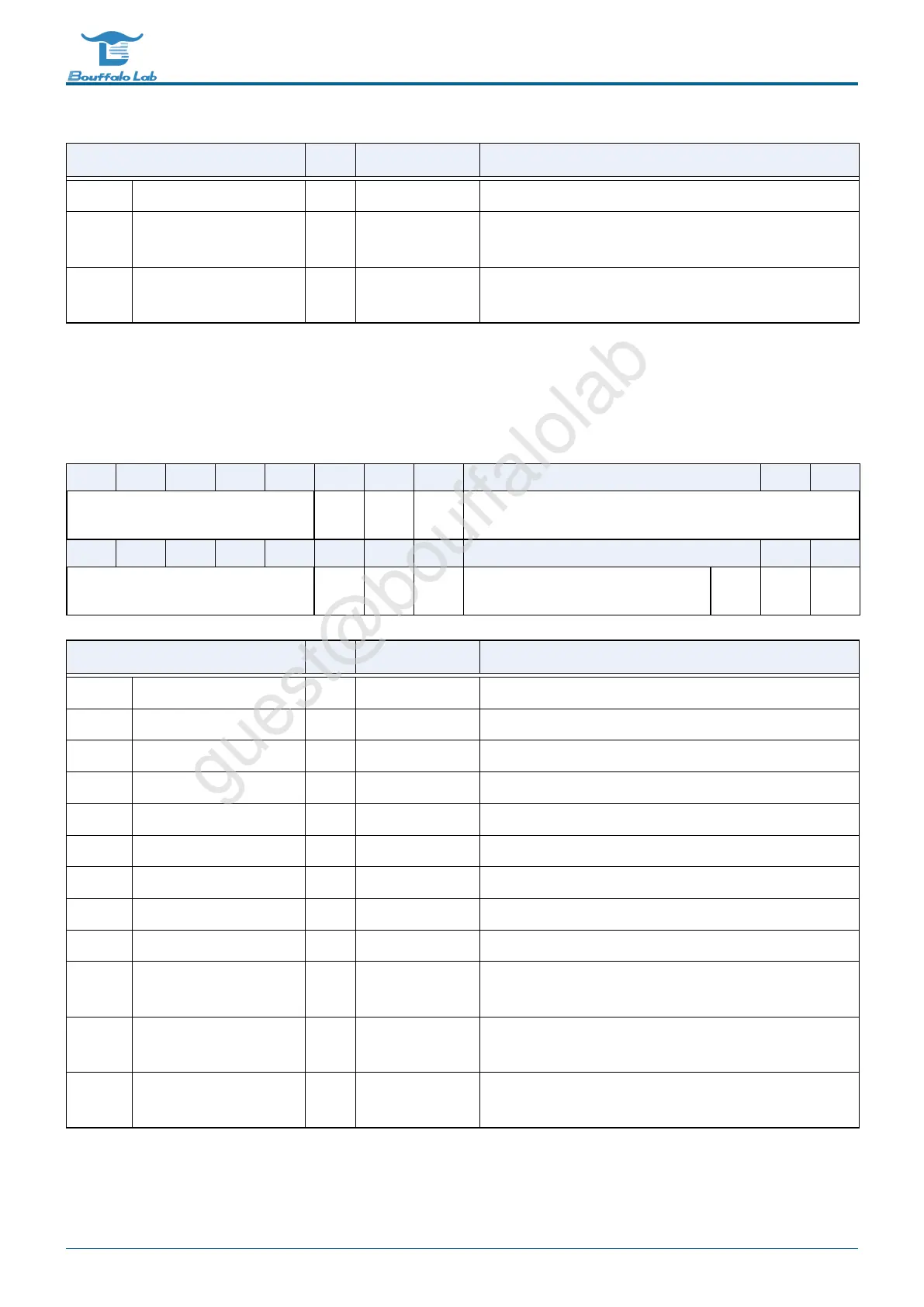

16.4.2 i2s_int_sts

Address:0x4000aa04

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD FER

EN

RXF

EN

TXF

EN

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD FER

MASK

RXF

MASK

TXF

MASK

RSVD FER

INT

RXF

INT

TXF

INT

Bits

Name Type Reset Description

31:27 RSVD

26 FEREN R/W 1’b1 Interrupt enable of i2s_fer_int

25 RXFEN R/W 1’b1 Interrupt enable of i2s_rxf_int

24 TXFEN R/W 1’b1 Interrupt enable of i2s_txf_int

23:11 RSVD

10 FERMASK R/W 1’b1 Interrupt mask of i2s_fer_int

9 RXFMASK R/W 1’b1 Interrupt mask of i2s_rxf_int

8 TXFMASK R/W 1’b1 Interrupt mask of i2s_txf_int

7:3 RSVD

2 FERINT R 1’b0 I2S TX/RX FIFO error interrupt, auto-cleared when FIFO

overflow/underflow error flag is cleared

1 RXFINT R 1’b0 I2S RX FIFO ready (rx_fifo_cnt > rx_fifo_th) interrupt, auto-

cleared when data is popped

0 TXFINT R 1’b0 I2S TX FIFO ready (tx_fifo_cnt > tx_fifo_th) interrupt, auto-

cleared when data is pushed

BL702/704/706 Reference Manual 284/ 375

@2021 Bouffalo Lab

Loading...

Loading...