BL702/704/706 Reference Manual

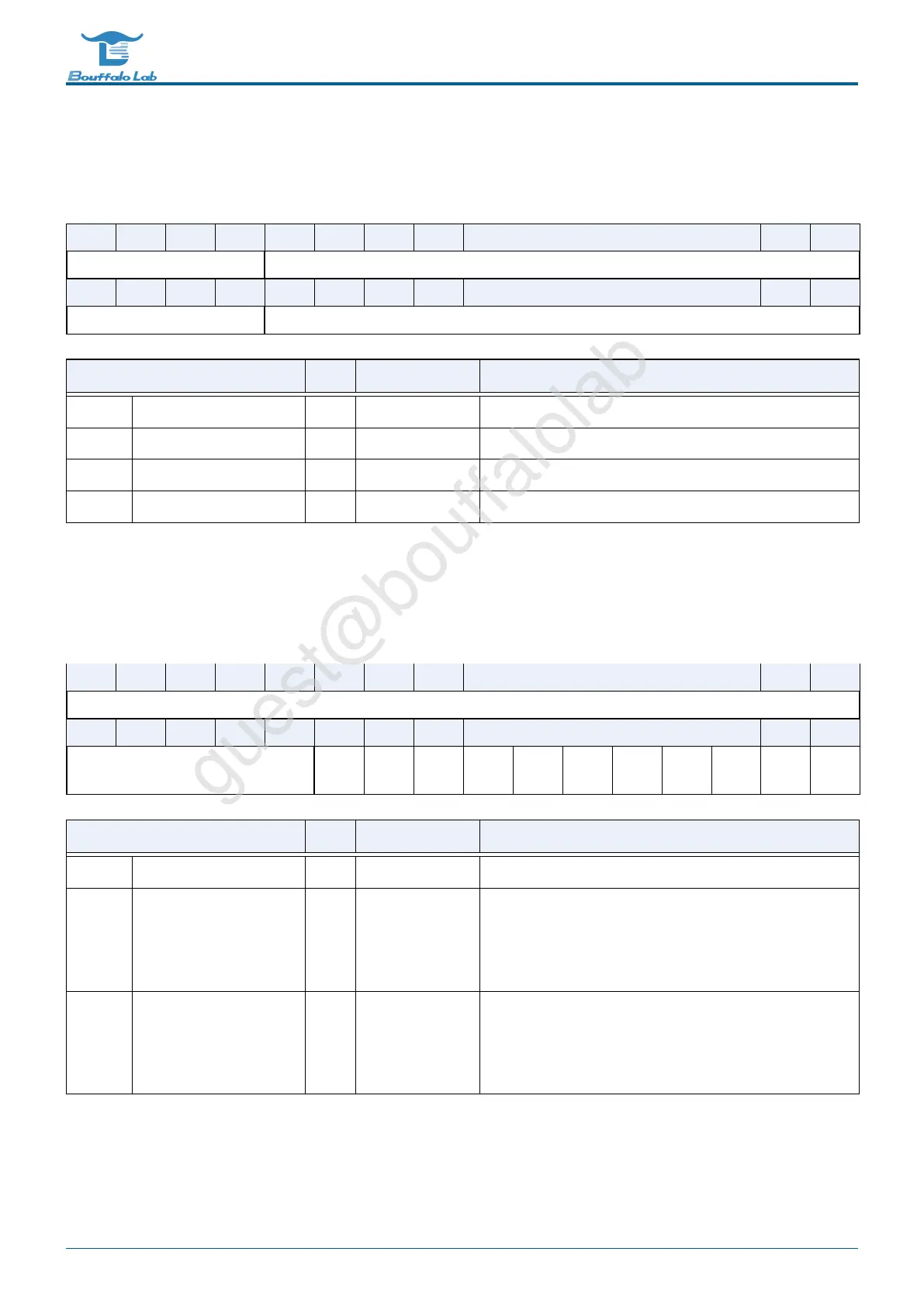

16.4.3 i2s_bclk_config

Address:0x4000aa10

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD BDIVH

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD BDIVL

Bits

Name Type Reset Description

31:28 RSVD

27:16 BDIVH R/W 12’d1 I2S BCLK active high period (unit: cycle of i2s_clk)

15:12 RSVD

11:0 BDIVL R/W 12’d1 I2S BCLK active low period (unit: cycle of i2s_clk)

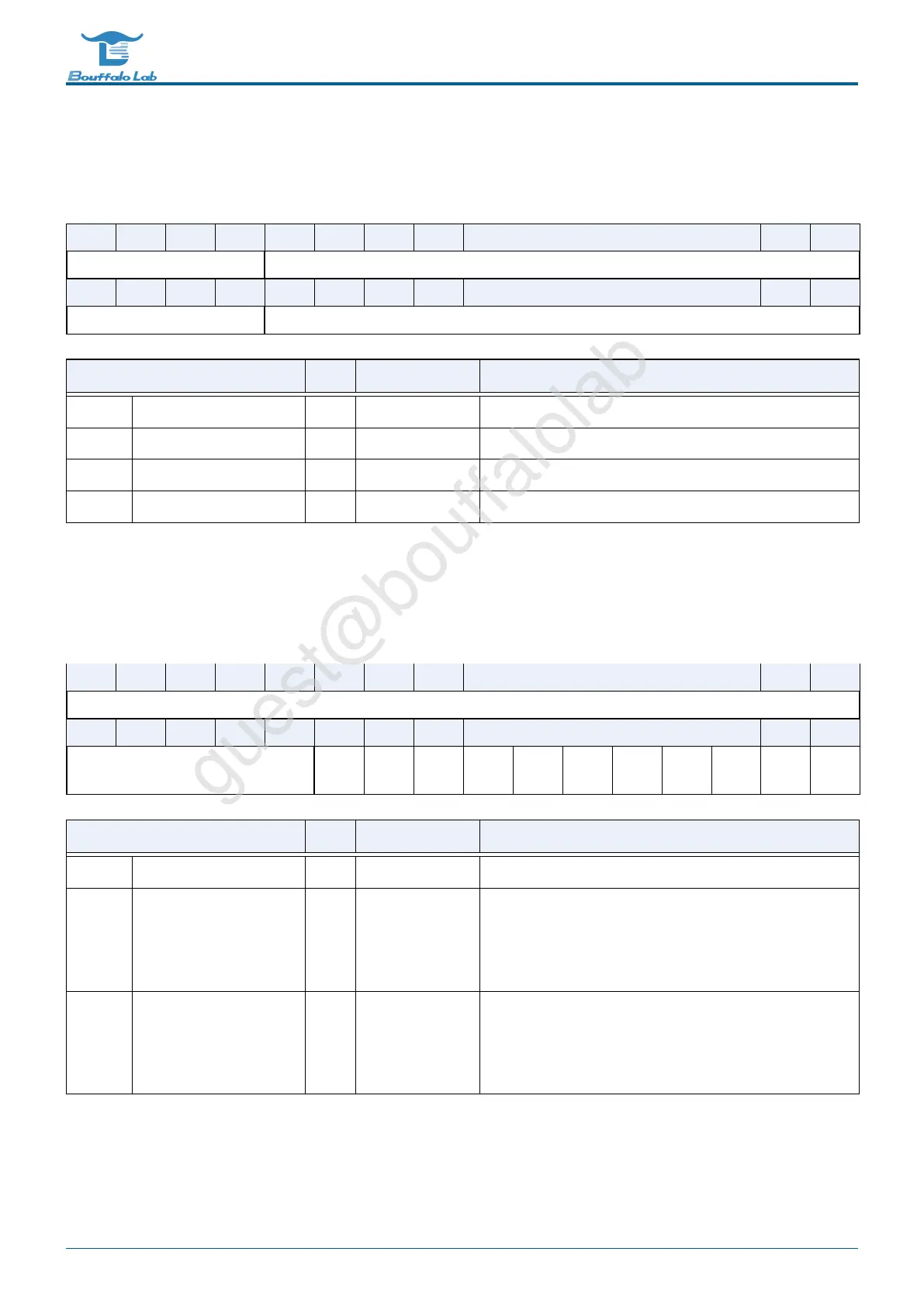

16.4.4 i2s_fifo_config_0

Address:0x4000aa80

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD 24B

LJ

LREC LRMG RUD

FLOW

RO

FLOW

TUD

FLOW

TO

FLOW

RXF

CLR

TXF

CLR

DMA

RXEN

DMA

TXEN

Bits

Name Type Reset Description

31:11 RSVD

10 24BLJ R/W 1’b0 FIFO 24-bit data left-justified mode

1’b0: Right-justified, 8’h0, data[23:0]

1’b1: Left-justified, data[23:0], 8’h0

Note: Valid only when cr_data_size = 2’d2 (24-bit)

9 LREC R/W 1’b0 The position of L/R channel data within each entry is ex-

changed if this bit is enabled

Can only be enabled if data size is 8 or 16 bits and csr_-

fifo_lr_merge is enabled

BL702/704/706 Reference Manual 285/ 375

@2021 Bouffalo Lab

Loading...

Loading...