BL702/704/706 Reference Manual

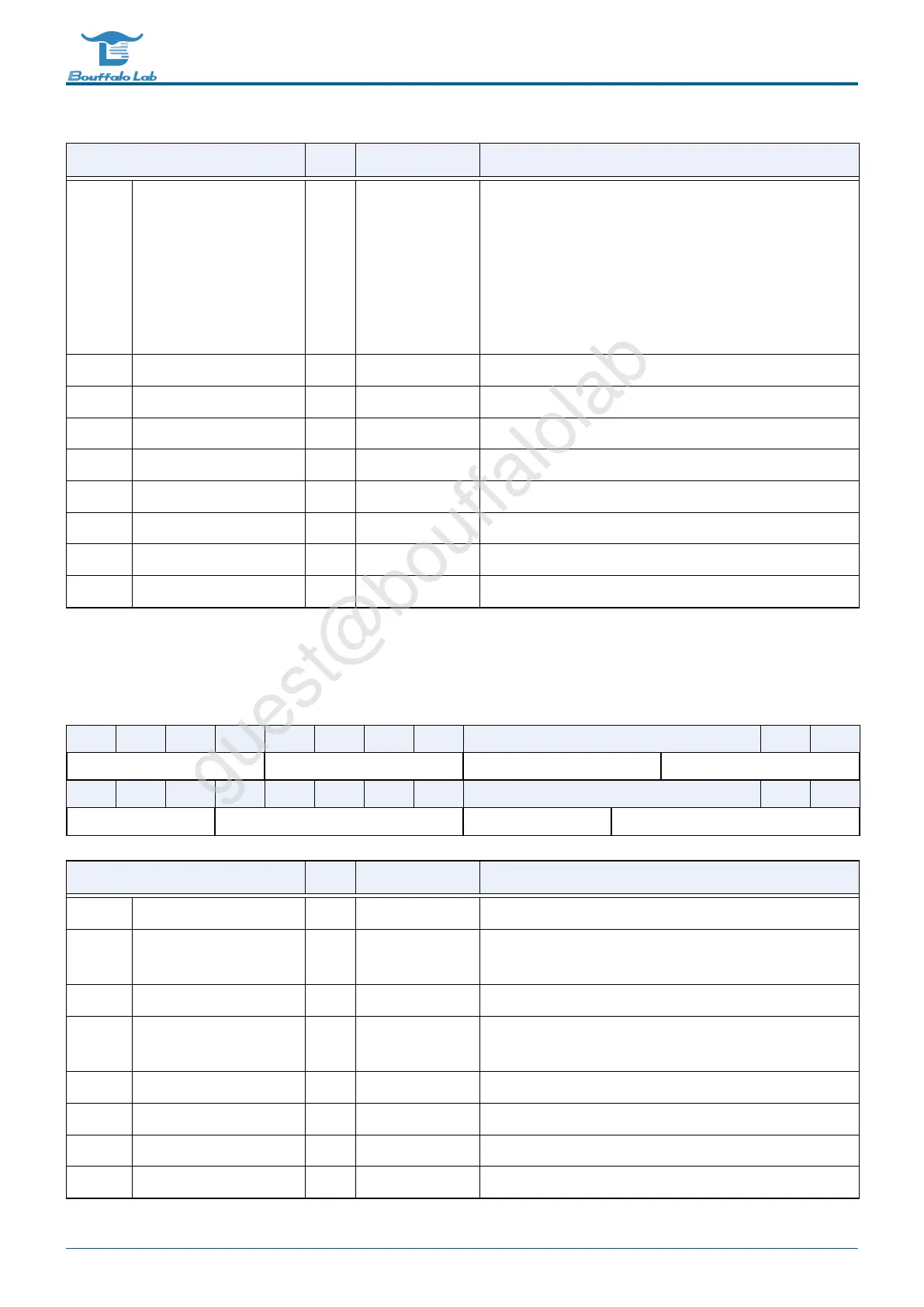

Bits

Name Type Reset Description

8 LRMG R/W 1’b0 Each FIFO entry contains both L/R channel data if this bit

is enabled

Can only be enabled if data size is 8 or 16 bits

Note: cr_fifo_lr_merge &cr_mono_mode should NOT be

enabled at the same time

Note: cr_fifo_lr_merge &cr_fifo_l_shift should NOT be en-

abled at the same time

7 RUDFLOW R 1’b0 Underflow flag of RX FIFO, can be cleared by rx_fifo_clr

6 ROFLOW R 1’b0 Overflow flag of RX FIFO, can be cleared by rx_fifo_clr

5 TUDFLOW R 1’b0 Underflow flag of TX FIFO, can be cleared by tx_fifo_clr

4 TOFLOW R 1’b0 Overflow flag of TX FIFO, can be cleared by tx_fifo_clr

3 RXFCLR W1C 1’b0 Clear signal of RX FIFO

2 TXFCLR W1C 1’b0 Clear signal of TX FIFO

1 DMARXEN R/W 1’b0 Enable signal of dma_rx_req/ack interface

0 DMATXEN R/W 1’b0 Enable signal of dma_tx_req/ack interface

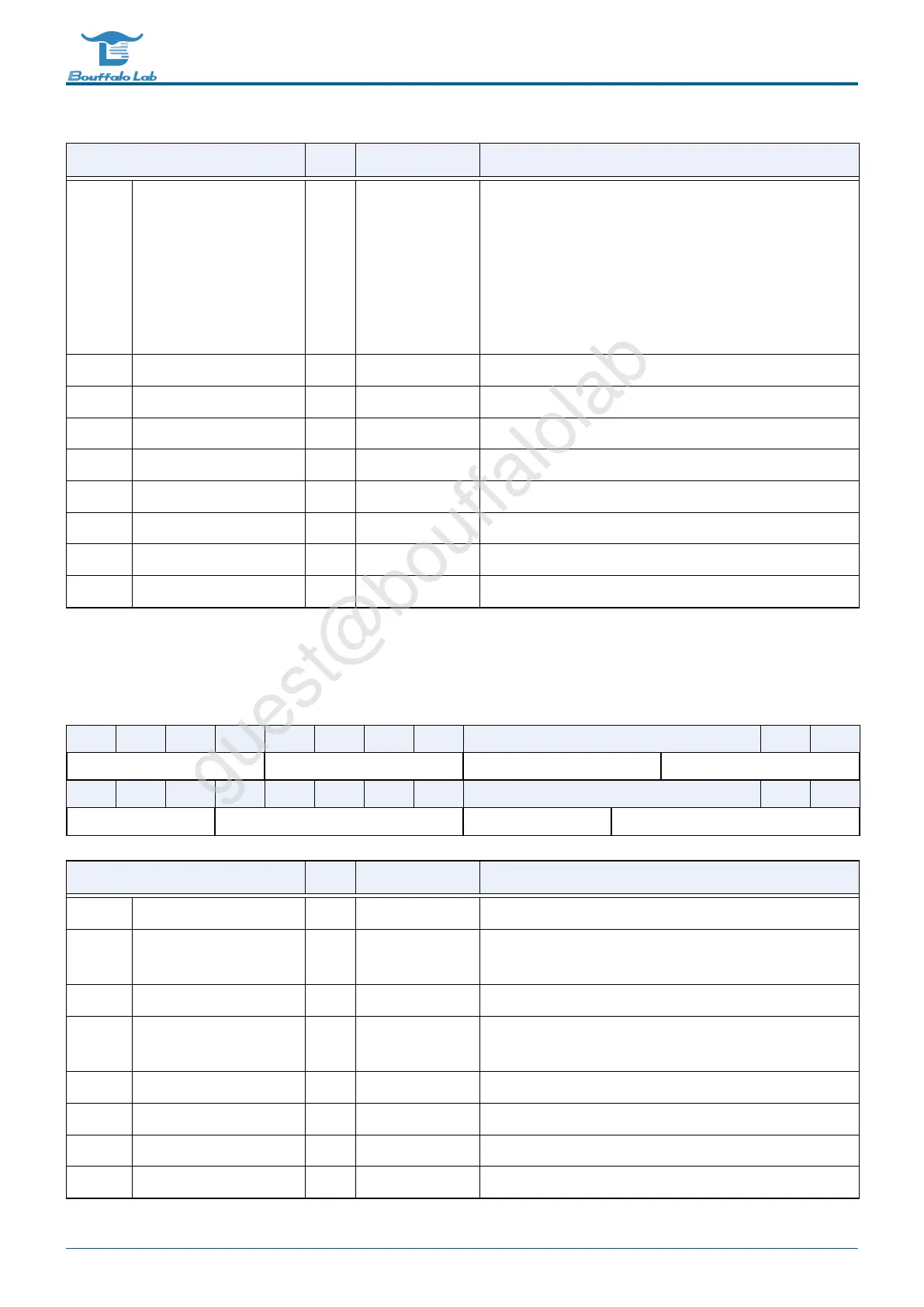

16.4.5 i2s_fifo_config_1

Address:0x4000aa84

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

RSVD RXTH RSVD TXTH

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RXCNT RSVD TXCNT

Bits

Name Type Reset Description

31:28 RSVD

27:24 RXTH R/W 4’d0 RX FIFO threshold, dma_rx_req will not be asserted if tx_-

fifo_cnt is less than this value

23:20 RSVD

19:16 TXTH R/W 4’d0 TX FIFO threshold, dma_tx_req will not be asserted if tx_-

fifo_cnt is less than this value

15:13 RSVD

12:8 RXCNT R 5’d0 RX FIFO available count

7:5 RSVD

4:0 TXCNT R 5’d16 TX FIFO available count

BL702/704/706 Reference Manual 286/ 375

@2021 Bouffalo Lab

Loading...

Loading...