EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

6-4

Program behavior is another important factor in determining cache efficiency. If a program uses

a piece of data only once, then the cache may spend all its time thrashing or replacing itself with

new data from memory. This is common in vector processing. The processor receives no added

efficiency from the cache because main memory is being requested frequently. In such instances,

the user can consider mapping the data entries as non-cacheable.

Cache system performance can be calculated based on the main memory access time, the cache

access time, the miss rate, and the write cycle time.

C

S

is defined as the ratio of the cache system access time to the main memory access time. C

S

is

a dimensionless number but provides a useful measure of the cache performance.

C

a

= (1-M)T

c

+ MT

m

C

s

= C

a

/T

m

= (1-M)(T

c

/T

m

) + M = (1-M)C

m

+M

where:

C

a

= average cache system cycle time averaged over reads and writes

T

c

= cache cycle time

T

m

= main memory cycle time

M = miss rate = 1-hit rate

C

s

= cache system access time as a fraction of main memory access time

C

m

= cache memory access time as compared to main memory cycle time

If the cache always misses, then M=1 and C

m

=1, and the main memory access is equal to the ef-

fective access time of the cache. If the cache is infinitely fast, then C

m

is equal to the miss rate.

Because the cache access time is finite, the cache system access time approaches the cache access

time as the miss rate approaches zero.

While the above discussion applies to read operations, it can be easily extended to write opera-

tions, which also affect system performance. When memory is written to, the CPU must wait for

the completion of the write cycle before proceeding to the next instruction. In a buffered memory

system, where posted writes occur, data can be loaded in a register, and the memory can be up-

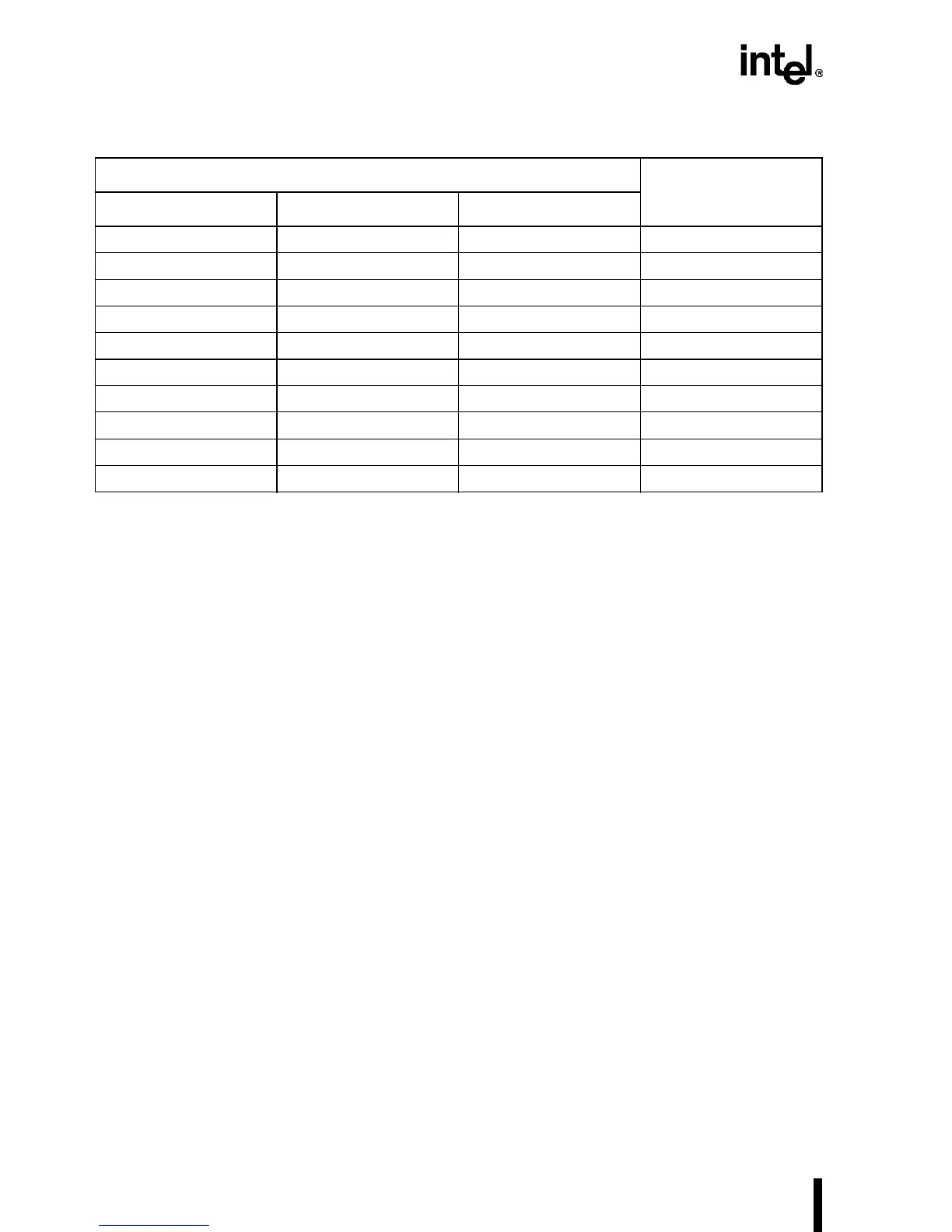

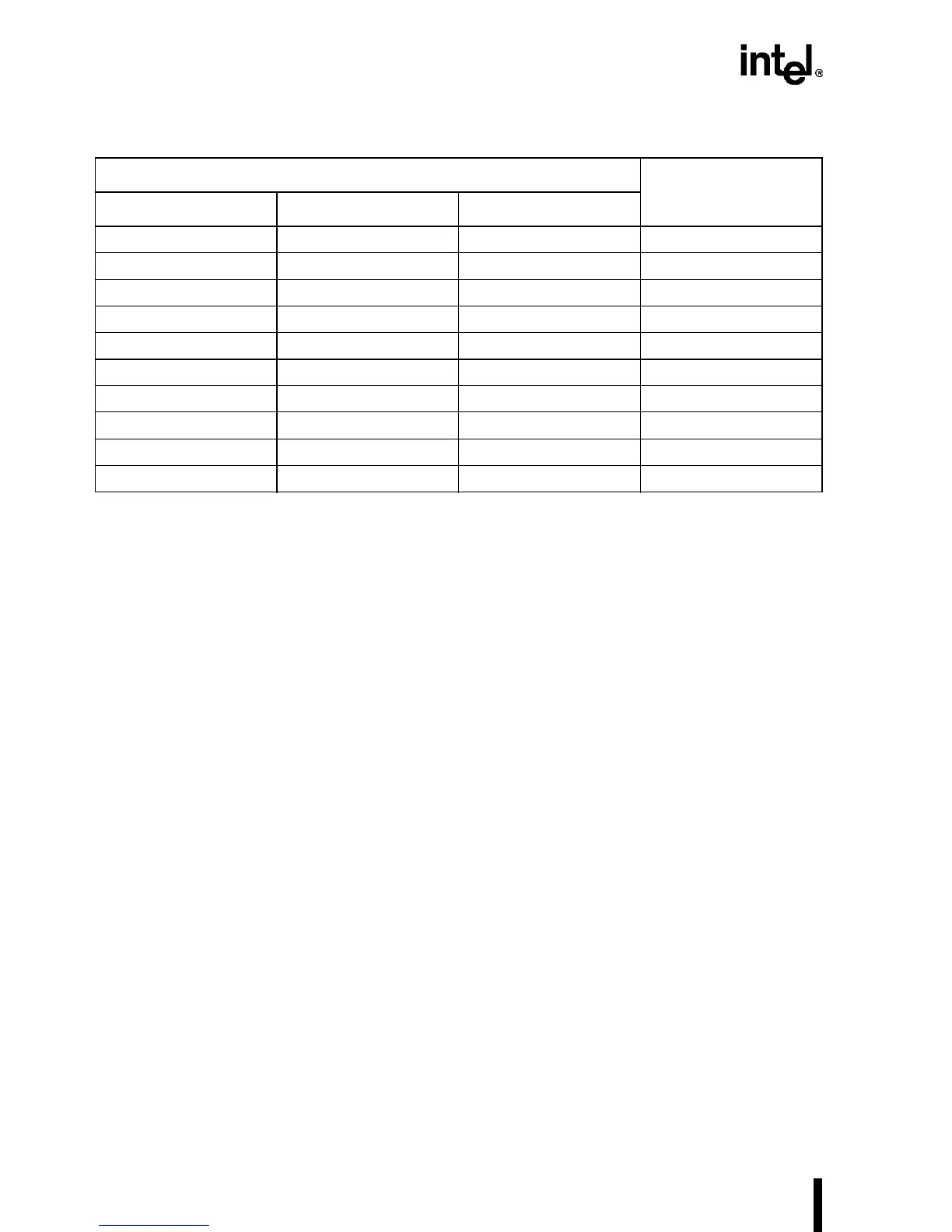

32 Kbyte 2-way 4 bytes 87%

32 Kbyte direct 8 bytes 91%

64 Kbyte direct 4 bytes 88%

64 Kbyte 2-way 4 bytes 89%

64 Kbyte 4-way 4 bytes 89%

64 Kbyte direct 8 bytes 92%

64 Kbyte 2-way 8 bytes 93%

128 Kbyte direct 4 bytes 89%

128 Kbyte 2-way 4 bytes 89%

128 Kbyte direct 8 bytes 93%

Table 6-1. Level-1 Cache Hit Rates (Sheet 2 of 2)

Cache Configurations

Hit Rate

Size Associativity Line Size

Loading...

Loading...