5-5

MEMORY SUBSYSTEM DESIGN

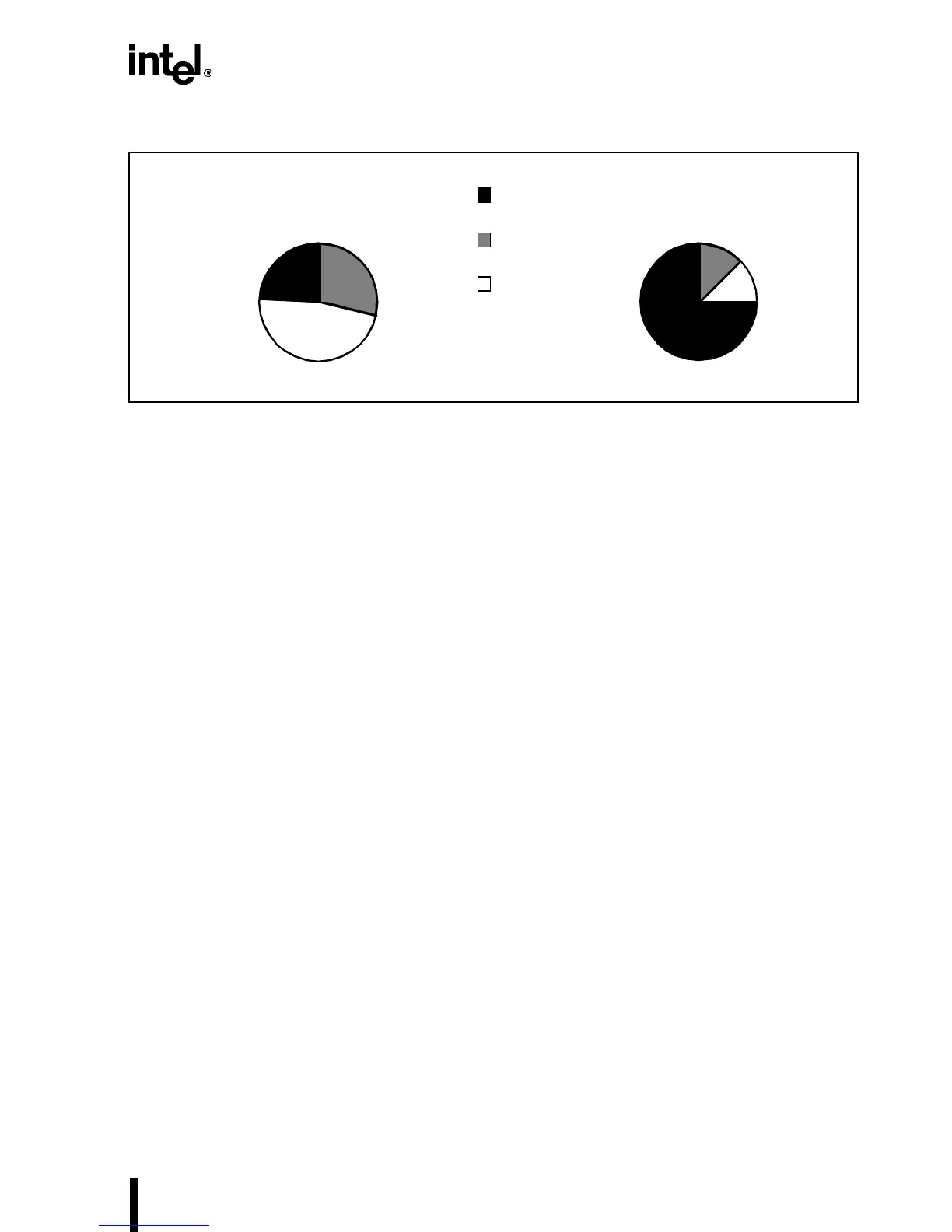

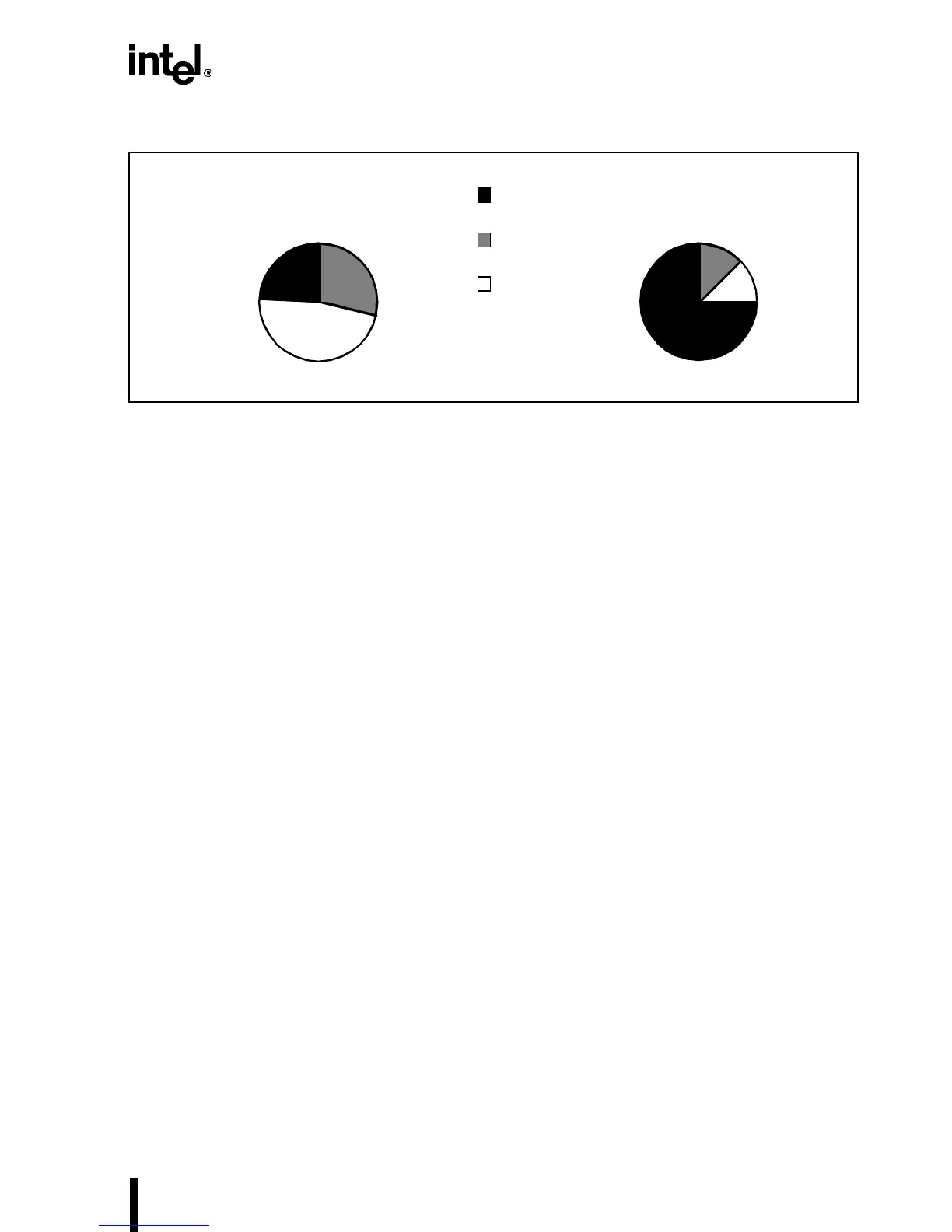

Figure 5-3. Intel386™ Processor Bus Cycle Mix/Intel486™ Processor Bus Cycle Mix

It seems obvious that many of these write cycles would be consecutive. In fact, 70% of all write

cycles are consecutive. Furthermore, 50% of all write cycles occur three in-a-row. It is obvious

from these statistics that optimizing the memory subsystem for write cycles can improve perfor-

mance. But it is important to optimize the memory system for consecutive write cycles. Improv-

ing individual write cycle latency does not buy much performance improvement if subsequent

write cycles suffer.

5.2.4 Improving Write Cycle Latency

5.2.4.1 Interleaving

The interleaving technique is used to support the burst bus feature of the Intel486 processor. The

use of this technique allows the DRAM to supply a dword every clock during burst cycles. Inter-

leaving proves to be very useful in Intel486 processor memory designs. Without its use, DRAM

timings such as T

PC

(Page Mode Cycle time) and T

CP

(CAS Precharge time) would prevent zero

wait state access at 33 MHz.

5.2.4.2 Write Posting

Analysis has shown that, in general, 6% degradation in performance can be expected for every

additional wait state added to write cycles. This analysis was performed by measuring the CPU

clocks required to execute several applications.

A technique called write posting can be used to improve write cycle latency. Write posting uses

data registers that hold write data during write cycles. This technique allows consecutive write

cycles to be overlapped. It also allows write cycles to be overlapped with L2 cache cycles and

reduces overall write miss latency.

Using the write posting technique adds complexity to the system logic. It is important to deter-

mine the performance improvement realized by using this technique. This question is especially

pertinent when we consider the logic already implemented in the Intel486 processor to improve

write performance. The internal Intel486 write buffers decouple the processor execution unit

from the external bus.

21.65%

35.90%

42.45%

74.84%

12.79%

12.37

Write

Prefetch

Read

Intel386™ Bus Cycle Mix Intel486™ Bus Cycle Mix

Loading...

Loading...