7-7

PERIPHERAL SUBSYSTEM

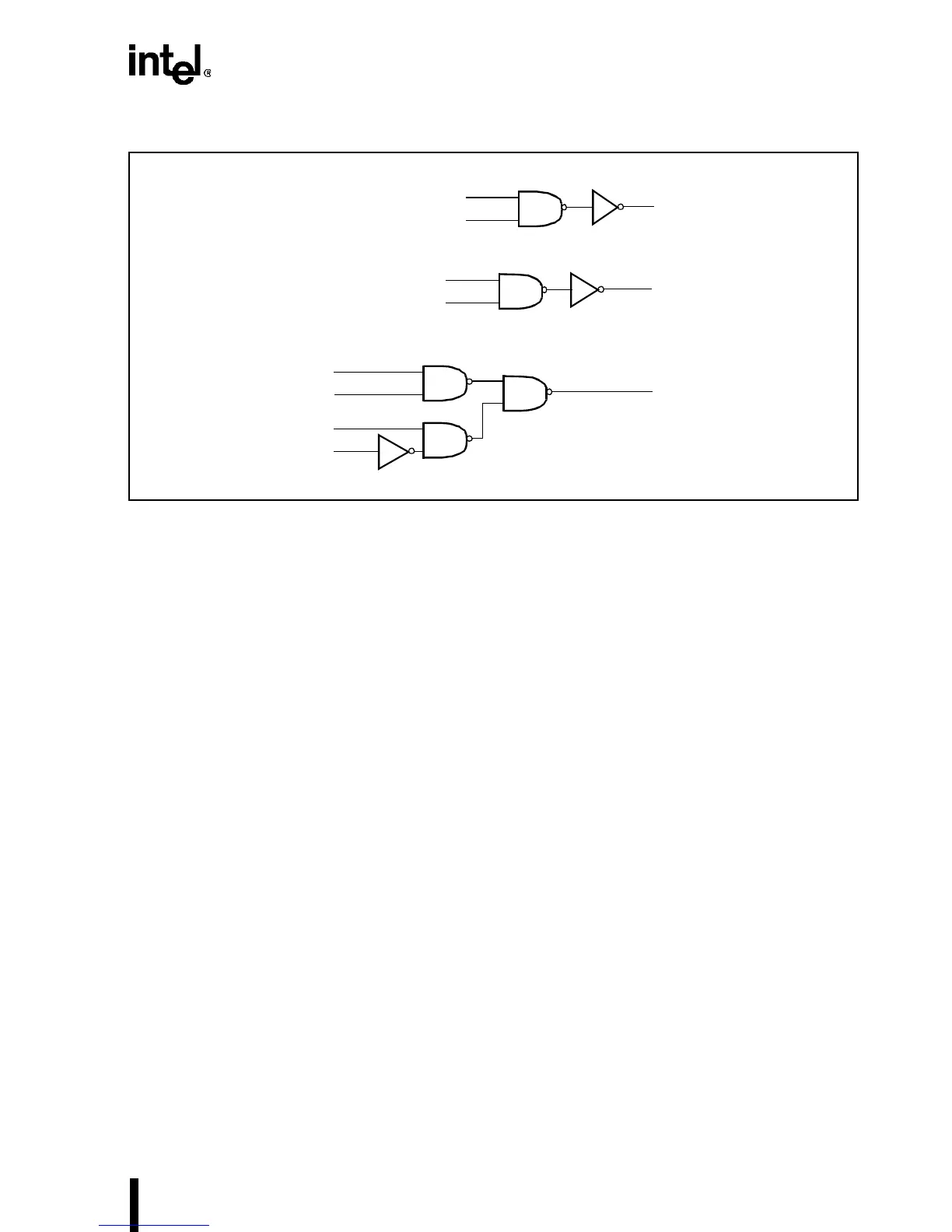

Figure 7-3. Logic to Generate A1, BHE# and BLE# for 16-Bit Buses

7.1.3.2 8-Bit I/O Interface

Due to the presence of dynamic data bus sizing and the variety of byte-enable pin combinations

(Table 7-2), byte swapping logic for 32-to-8-bit conversions can be implemented in various ways.

This section discusses an example in which BE3#–BE0# are low and D7–D0 are used when BS8#

is enabled.

Figure 7-4 shows the interfacing of an Intel486 processor to an 8-bit device. This implementation

requires seven 8-bit bidirectional data buffers.

A1

BE0#

BE1#

BHE#

BE1#

BE3#

BE0#

BE2#

BE0#

BE1#

BLE# (OR A0)

Loading...

Loading...