4-23

BUS OPERATION

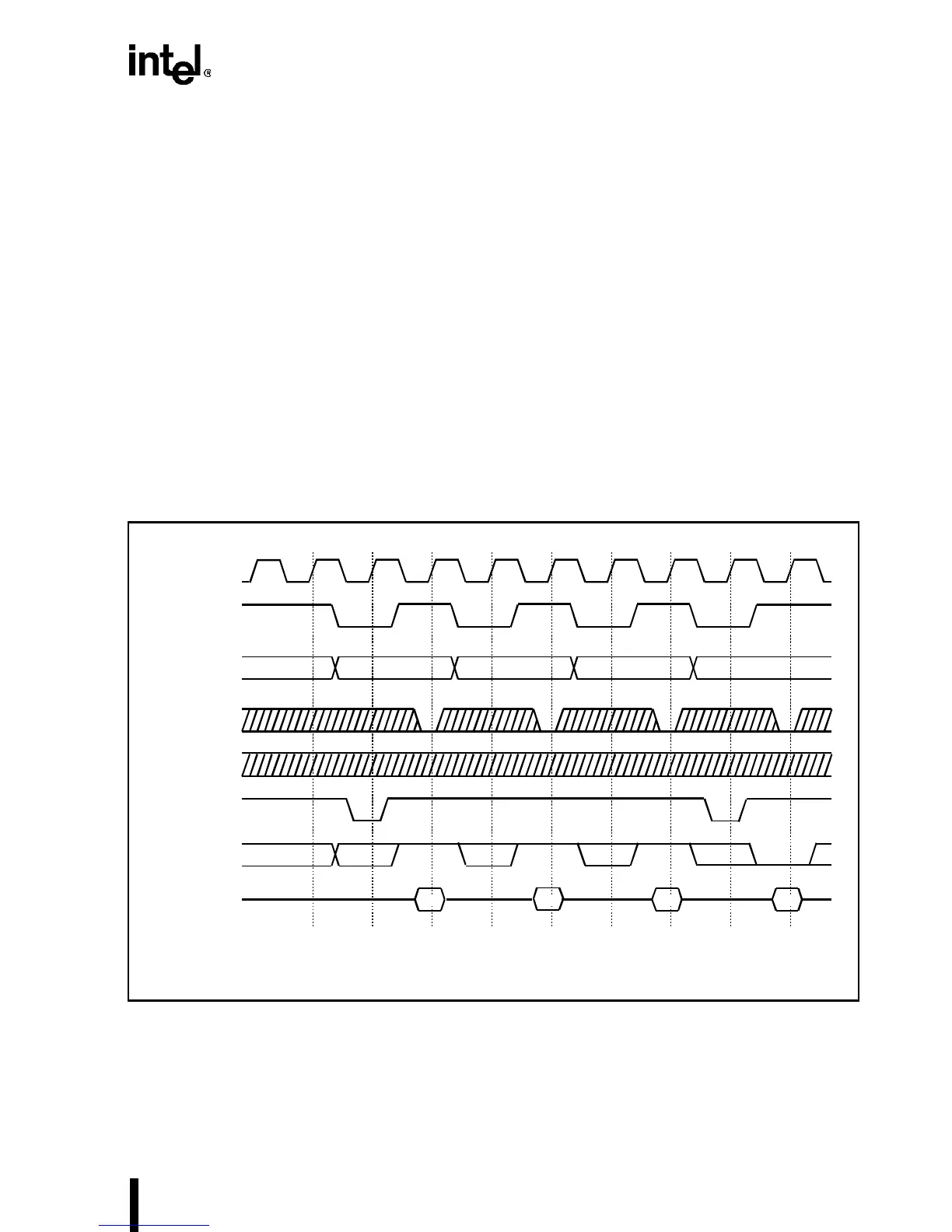

4.3.3.2 Non-Burst Cacheable Cycles

Figure 4-14 shows a non-burst cacheable cycle. The cycle becomes a cache fill when the Intel486

processor samples KEN# asserted at the end of the first clock. The Intel486 processor deasserts

BLAST# in the second clock in response to KEN#. BLAST# is deasserted because a cache fill

requires three additional cycles to complete. BLAST# remains deasserted until the last transfer

in the cache line fill. KEN# must be asserted in the last cycle of the transfer for the data to be

written into the internal cache.

Note that this cycle would be a single bus cycle if KEN# was not sampled asserted at the end of

the first clock. The subsequent three reads would not have happened since a cache fill was not

requested.

The BLAST# output is invalid in the first clock of a cycle. BLAST# may be asserted during the

first clock due to earlier inputs. Ignore BLAST# until the second clock.

During the first cycle of the cache line fill the external system should treat the byte enables as if

they are all asserted. In subsequent cycles in the burst, the Intel486 processor drives the address

lines and byte enables. (See Section 4.3.4.2, “Burst and Cache Line Fill Order.”)

Figure 4-14. Non-Burst, Cacheable Cycles

CLK

ADS#

A31–A2

M/IO#

D/C#

W/R#

BE3#–BE0#

KEN#

RDY#

BLAST#

DATA

Ti T1 T2 T1 T2 T1 T2 T1 T2 Ti

†

To Processor

BRDY#

†

†

††

242202-035

Loading...

Loading...