9-7

PERFORMANCE CONSIDERATIONS

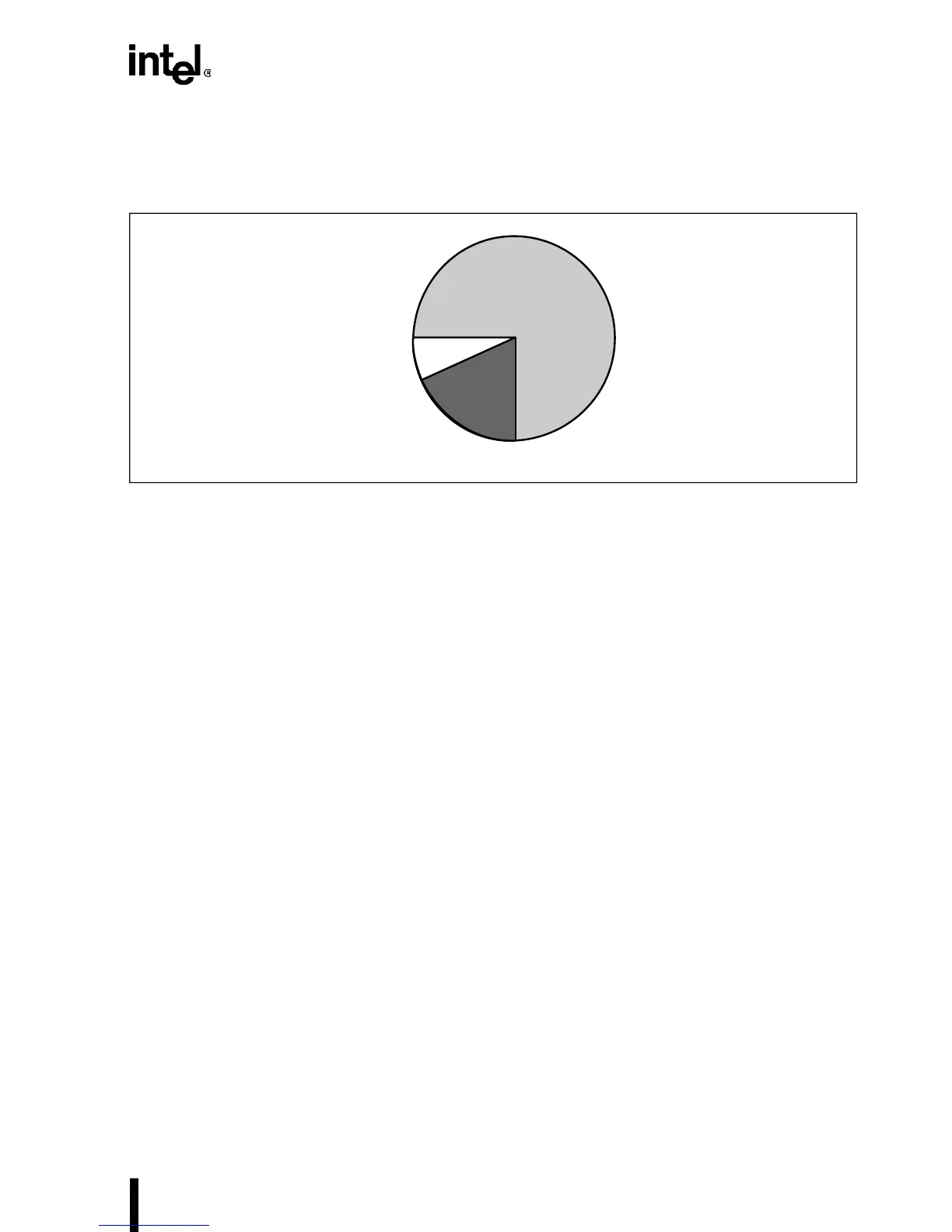

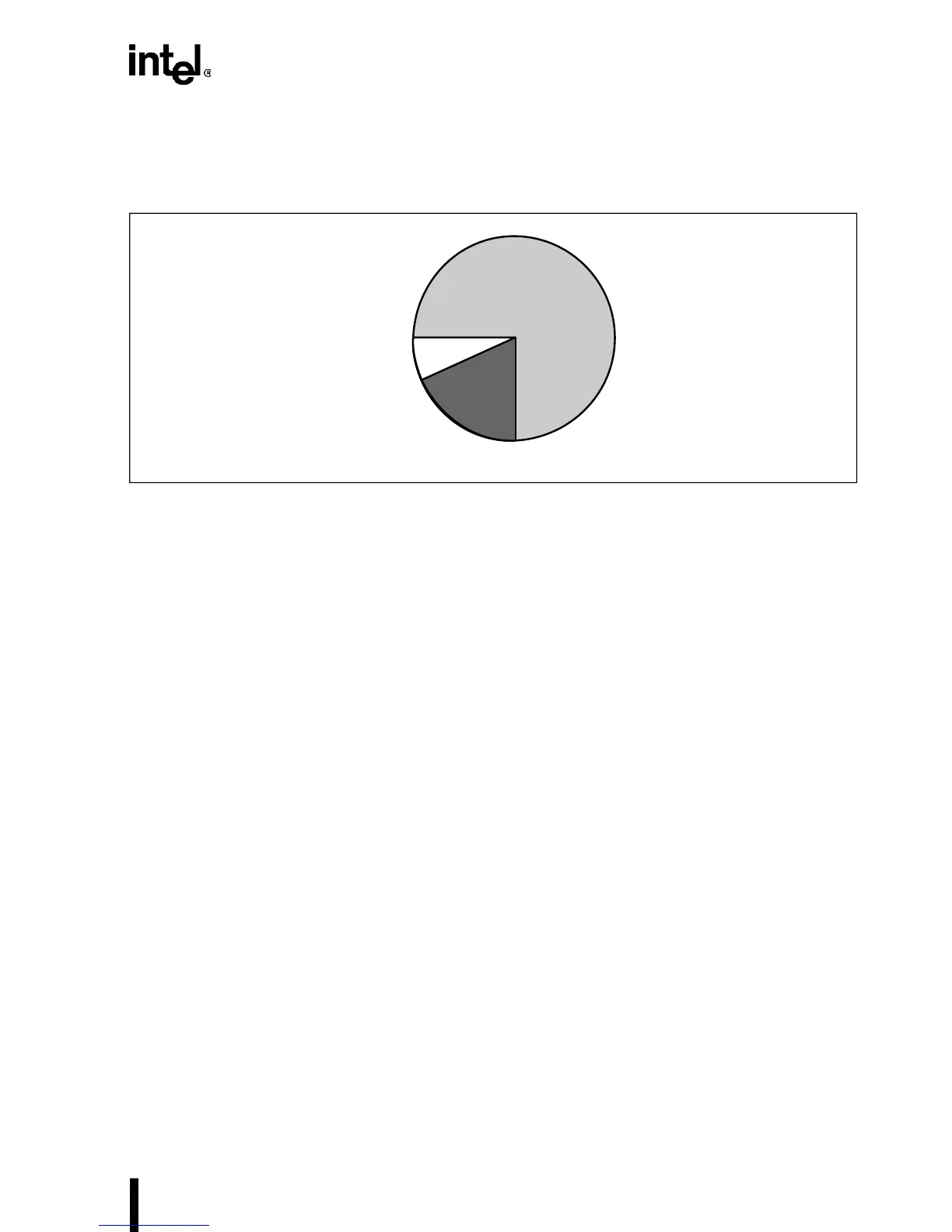

bus cycles, as shown in Figure 9-3. For best performance, memory systems that use the Intel486

processor should be optimized for write cycles.

Figure 9-2. Intel486™ Processor Bus Cycle Mix with On-Chip Cache

9.4 ON-CHIP WRITE BUFFERS

As previously discussed, low write latency is more critical for Intel486 processor systems than in

previous processors. The Intel486 processor has four write buffers to allow CPU execution with-

out latency for write operations. The buffers can be filled at the rate of one per clock cycle until

all four are filled.

When all four write buffers are empty and the bus is idle, a write request propagates to the exter-

nal bus, bypassing the write buffers directly. If the bus is not available when the write cycle is

generated internally, then the write is buffered and propagated as soon as the bus is available. If

a cache hit occurs on a write, then the on-chip cache is updated immediately.

Writes are normally executed on the external bus in the same order in which they are received by

the write buffers, as in a FIFO. Under certain conditions a memory read can take priority, and the

sequence of external bus cycles can be reordered, even though the writes occurred earlier in pro-

gram execution.

A memory read will only be reordered before all writes under the following conditions. If all

writes in the buffers are cache hits and the read is a cache miss, then the read is guaranteed not to

conflict with the pending writes. In this case, the bus cycles can be reordered to allow the read

operation to occur before the write buffers have been retired.

Intel486 processor performance is enhanced because of the write buffers and bus cycle reorder-

ing. The write buffers decouple the internal execution unit from the bus. Program execution can

continue without delay of write latency. In addition, reordering allows program execution to con-

tinue in some cases even if some write buffers are filled.

A5441-01

Writes

77%

Reads

8%

Prefetches

15%

Loading...

Loading...