EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

9-6

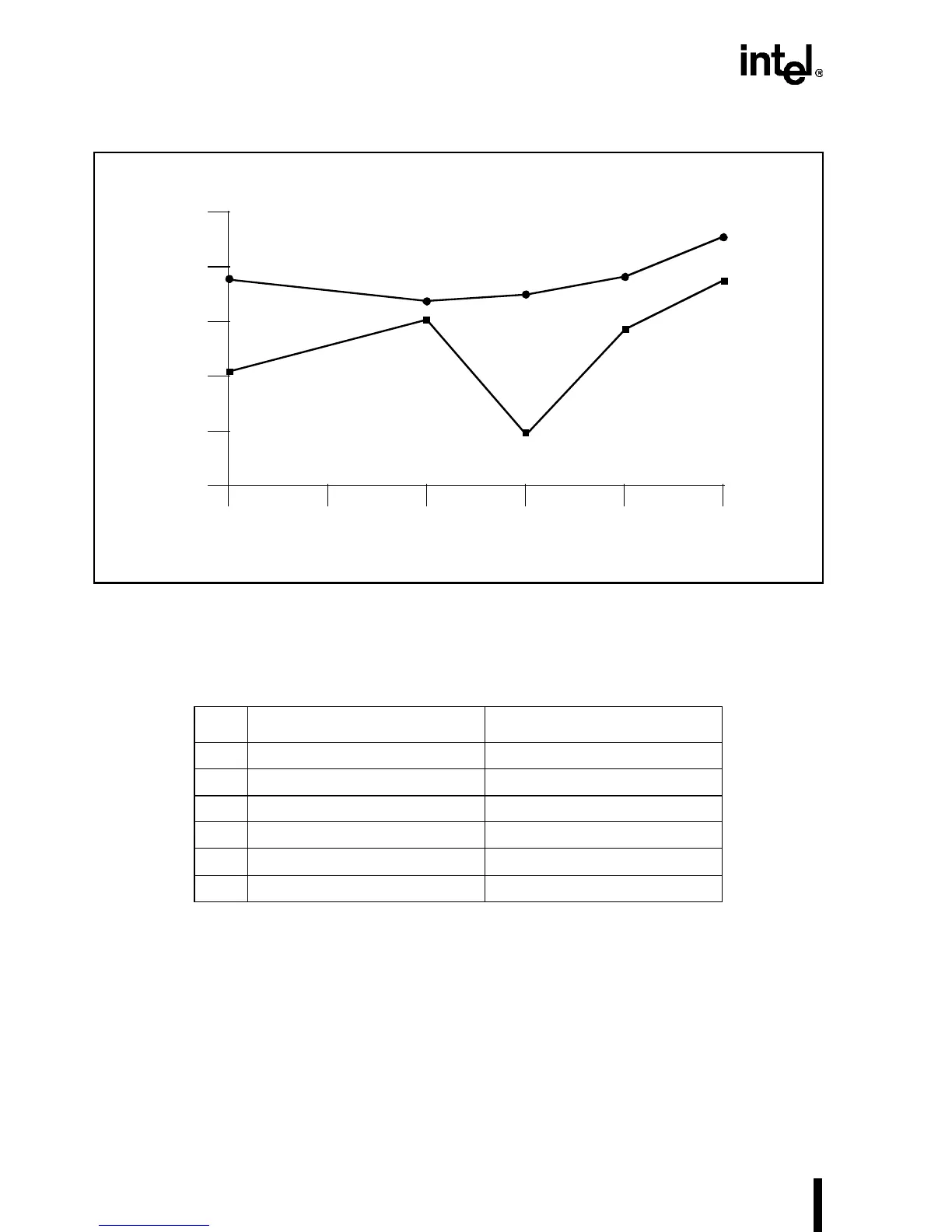

Figure 9-1. Cache Hit Rate for Various Programs

9.3.3 Bus Cycle Mix with and without On-Chip Cache

Microprocessors that lack an on-chip cache must devote a significant portion of execution time

to external bus accesses. Code prefetches and data reads must come from the external memory

system; subsequently a high percentage of bus accesses are reads. Traditional memory systems

are optimized for reads because of this mix of bus cycles.

With the Intel486 processor’s on-chip cache, however, the high hit rate reduces the number of ex-

ternal reads. As the on-chip cache implements a write-through policy, the number of writes to the

bus is not reduced. As a result, external bus read cycles are now a minor portion of the overall

Table 9-2. Programs Used

Name Description

A FRAME Desktop publishing package

B PHONGS4 Small benchmark program

C Sunview Window manager

D INVFRAME Desktop publishing package

E TPASCAL Pascal compiler

F TROFF Text Formatter

On-Chip Cache Hit Rates

A

BC

D

E

75.00%

80.00%

85.00%

90.00%

95.00%

100.00%

Hit Rate

Program

Prefetches

Reads

Loading...

Loading...