4-21

BUS OPERATION

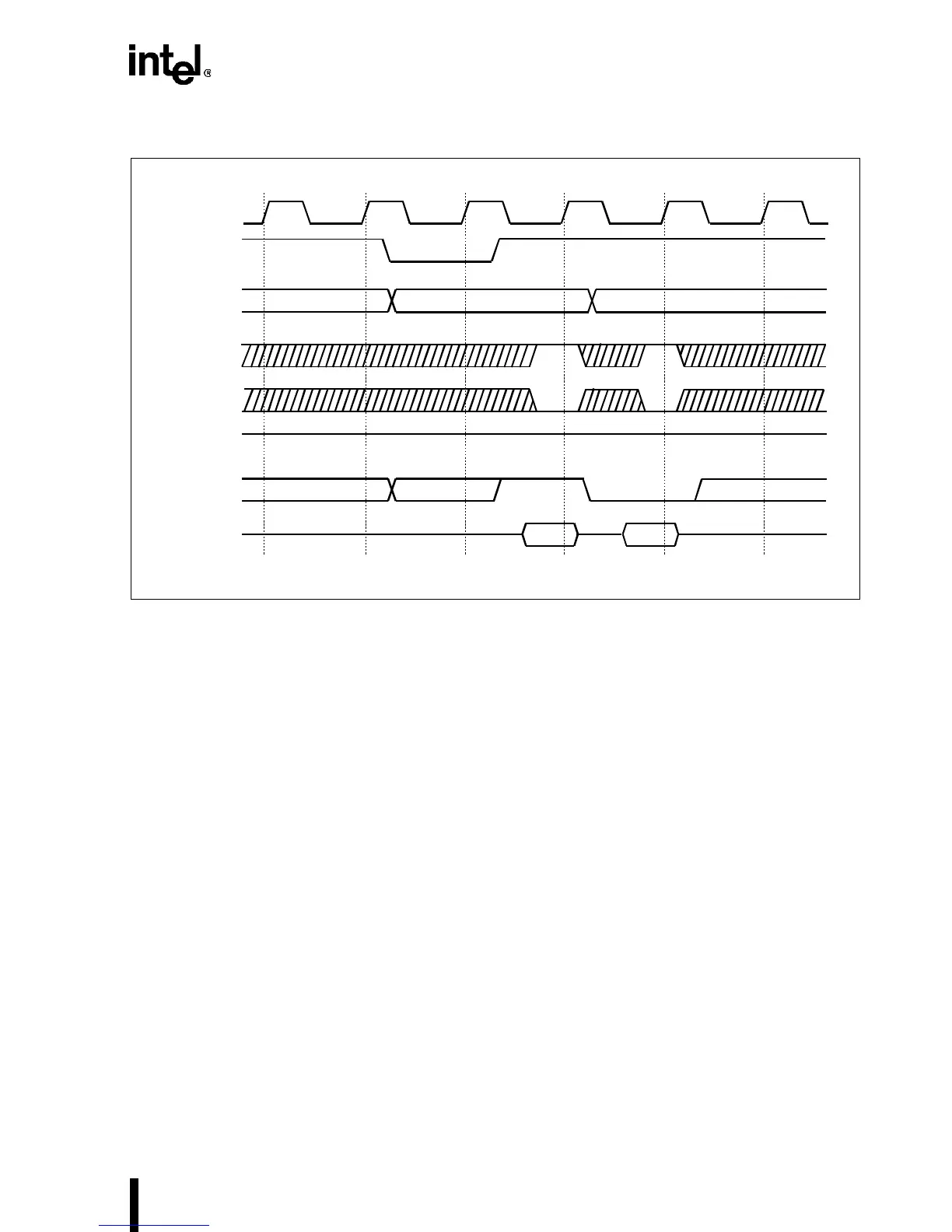

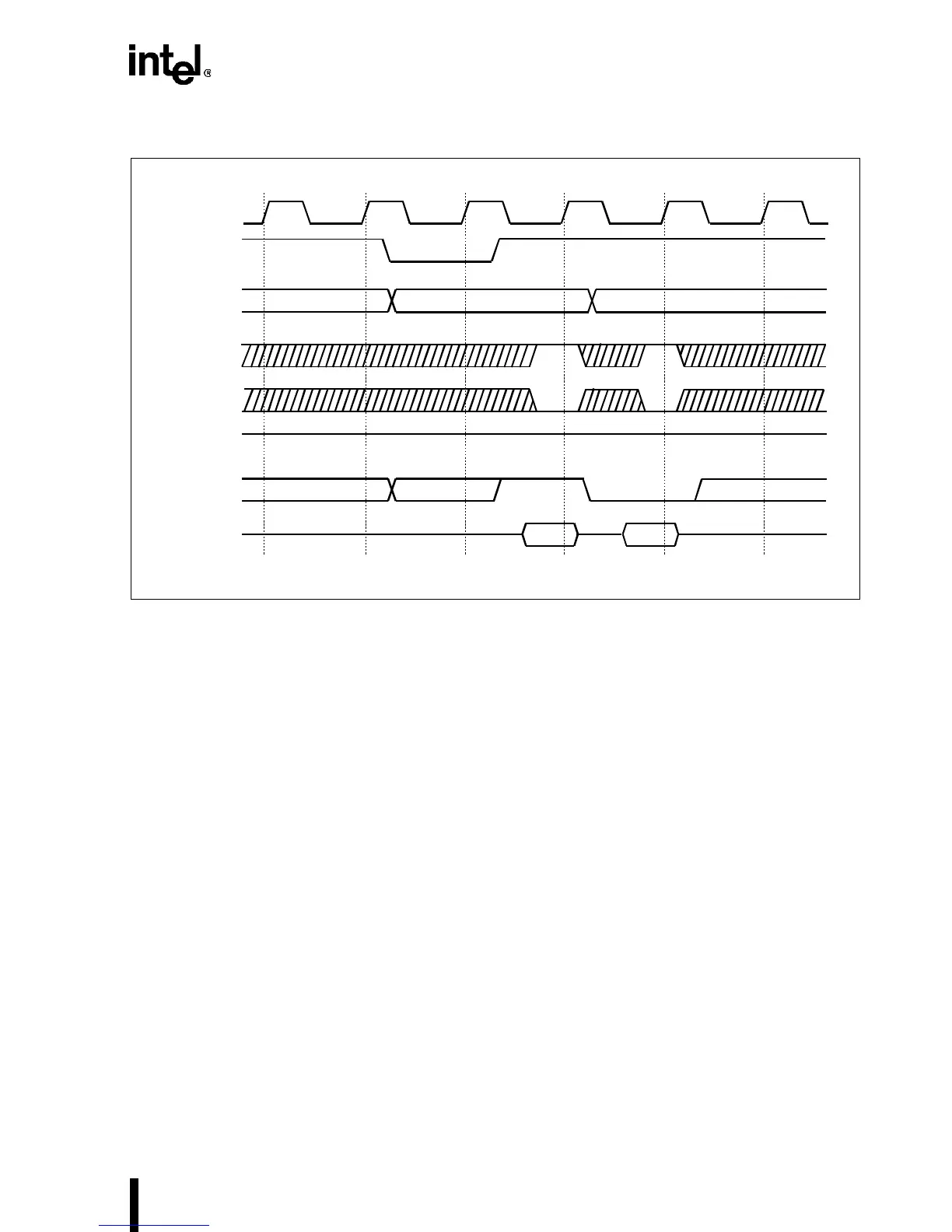

Figure 4-13. Non-Cacheable Burst Cycle

4.3.3 Cacheable Cycles

Any memory read can become a cache fill operation. The external memory system can allow a

read request to fill a cache line by asserting KEN# one clock before RDY# or BRDY# during the

first cycle of the transfer on the external bus. Once KEN# is asserted and the remaining three re-

quirements described below are met, the Intel486 processor fetches an entire cache line regard-

less of the state of KEN#. KEN# must be asserted in the last cycle of the transfer for the data to

be written into the internal cache. The Intel486 processor converts only memory reads or

prefetches into a cache fill.

KEN# is ignored during write or I/O cycles. Memory writes are stored only in the on-chip cache

if there is a cache hit. I/O space is never cached in the internal cache.

To transform a read or a prefetch into a cache line fill, the following conditions must be met:

1. The KEN# pin must be asserted one clock prior to RDY# or BRDY# being asserted for the

first data cycle.

2. The cycle must be of a type that can be internally cached. (Locked reads, I/O reads, and

interrupt acknowledge cycles are never cached.)

3. The page table entry must have the page cache disable bit (PCD) set to 0. To cache a page

table entry, the page directory must have PCD=0. To cache reads or prefetches when

CLK

ADS#

A31–A2

M/IO#

D/C#

W/R#

BE3#–BE0#

RDY#

BRDY#

BLAST#

DATA

KEN#

TiT2T1T2T1Ti

To Processor

†

†

†

242202-034

Loading...

Loading...