7-45

PERIPHERAL SUBSYSTEM

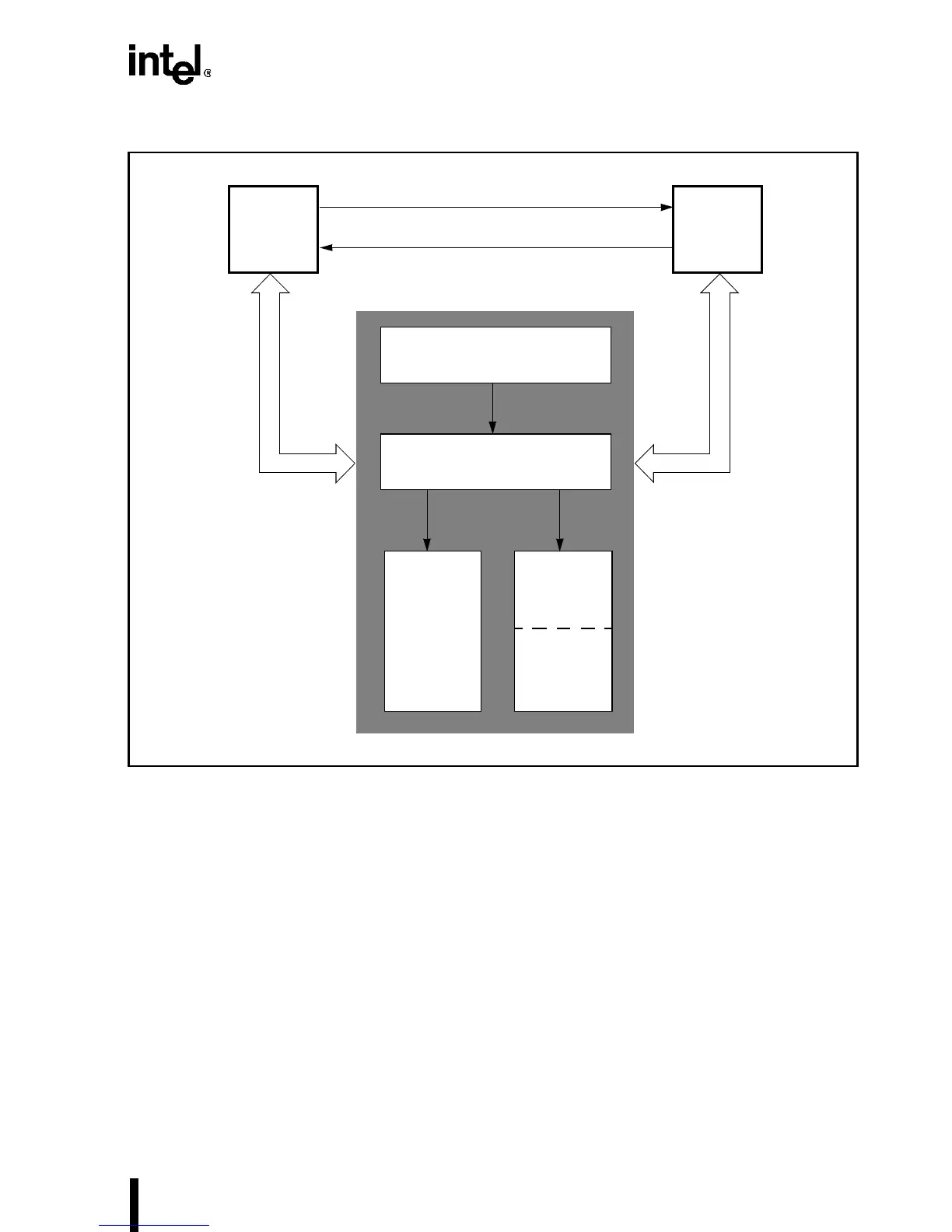

Figure 7-24. 82596 Shared Memory

The coprocessor executes its command list from shared memory and, in parallel, receives frames

from the network and places them in shared memory. The processor manages the shared memory,

which contains command chains and bidirectional data chains. The coprocessor executes the

command chains. An on-chip DMA controls four channels, which allow autonomous transfers of

data blocks independently of the processor. Buffers containing erroneous or collided frames can

be automatically recovered without processor intervention. The processor becomes involved only

after a command sequence has finished executing, or after a sequence of frames has been received

and stored, ready for processing.

In addition to this normal operating mode, the processor can initiate a port access in the copro-

cessor. This mode may be entered whenever the coprocessor is not actively driving the bus. It

allows the processor to write an alternate system configuration pointer, write an alternate dump

command and pointer (used for troubleshooting a no-response problem), perform a software re-

set, or perform a self-test.

82596

LAN

Controller

Intel486™

INTA#

Processor

Initialization

Root

System Control

Block Mailbox

Shared Memory

INT/INT#

Receive

Frame

Area

Command

Line

Transmit

Buffer

Loading...

Loading...