4-11

BUS OPERATION

The function of unaligned transfers with dynamic bus sizing is not obvious. When the external

systems asserts BS16# or BS8#, forcing extra cycles, low-order bytes or words are transferred

first (opposite to the example above). When the Intel486 processor requests a 4-byte read and the

external system asserts BS16#, the lower two bytes are read first followed by the upper two bytes.

In the unaligned transfer described above, the processor requested three bytes on the first cycle.

When the external system asserts BS16# during this 3-byte transfer, the lower word is transferred

first followed by the upper byte. In the final cycle, the lower byte of the 4-byte operand is trans-

ferred, as shown in the 32-bit example above.

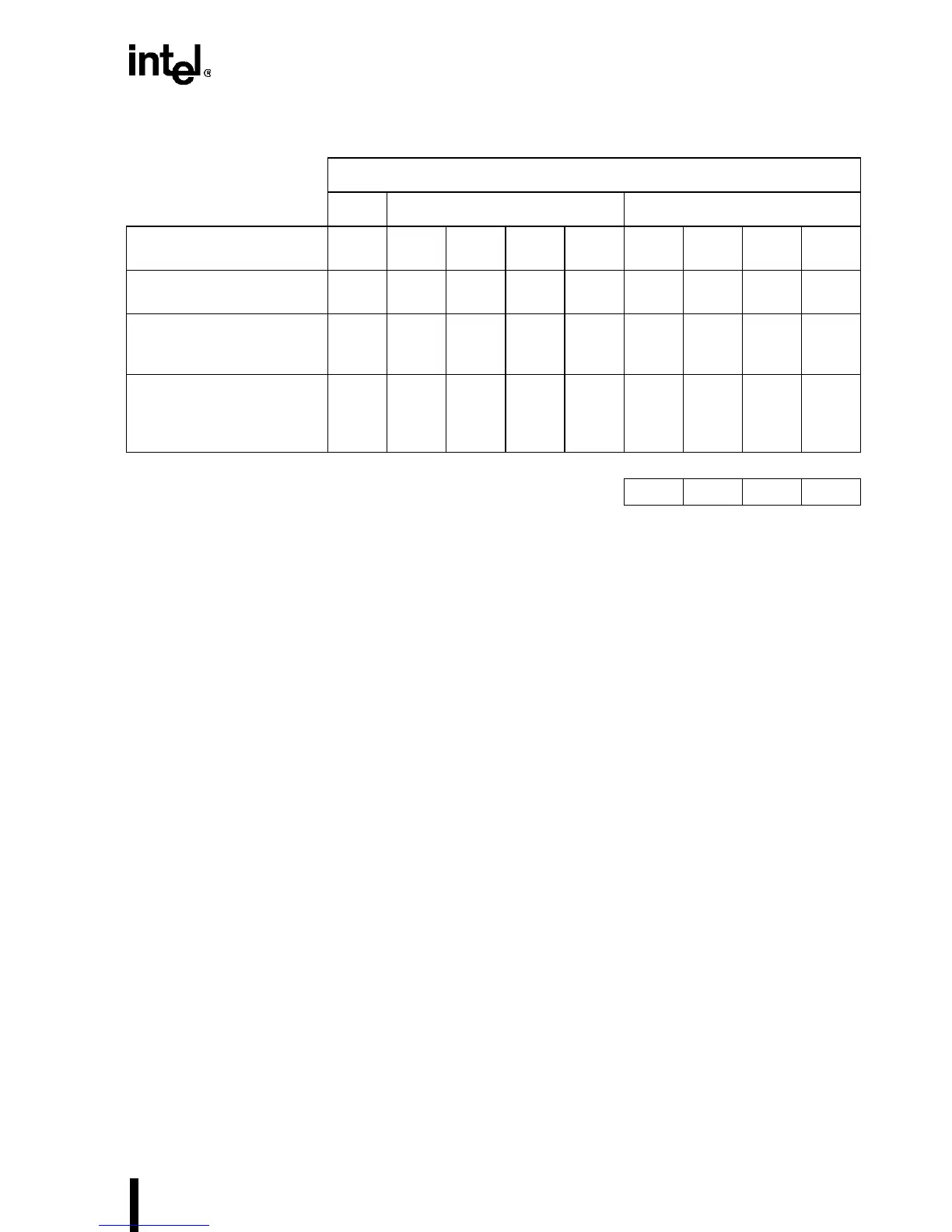

Table 4-7. Transfer Bus Cycles for Bytes, Words and Dwords

Byte-Length of Logical Operand

12 4

Physical Byte Address in

Memory (Low Order Bits)

xx 00 01 10 11 00 01 10 11

Transfer Cycles over 32-Bit

Bus

bwwwhb

lb

dhb

l3

hw

lw

h3

lb

Transfer Cycles over 16-Bit

Bus

(

†

= BS#16 asserted)

bwlb

†

hb

†

whb

lb

lw

†

hw

†

hb

lb

†

mw

†

hw

lw

mw

†

hb

†

lb

Transfer Cycles over 8-Bit

Bus

(

‡

= BS8# Asserted)

blb

‡

hb

‡

lb

‡

hb

‡

lb

‡

hb

‡

hb

lb

lb

‡

mlb

‡

mhb

‡

hb

‡

hb

lb

‡

mlb

‡

mhb

‡

mhb

‡

hb

‡

lb

‡

mlb

‡

mlb

‡

mhb

‡

hb

‡

lb

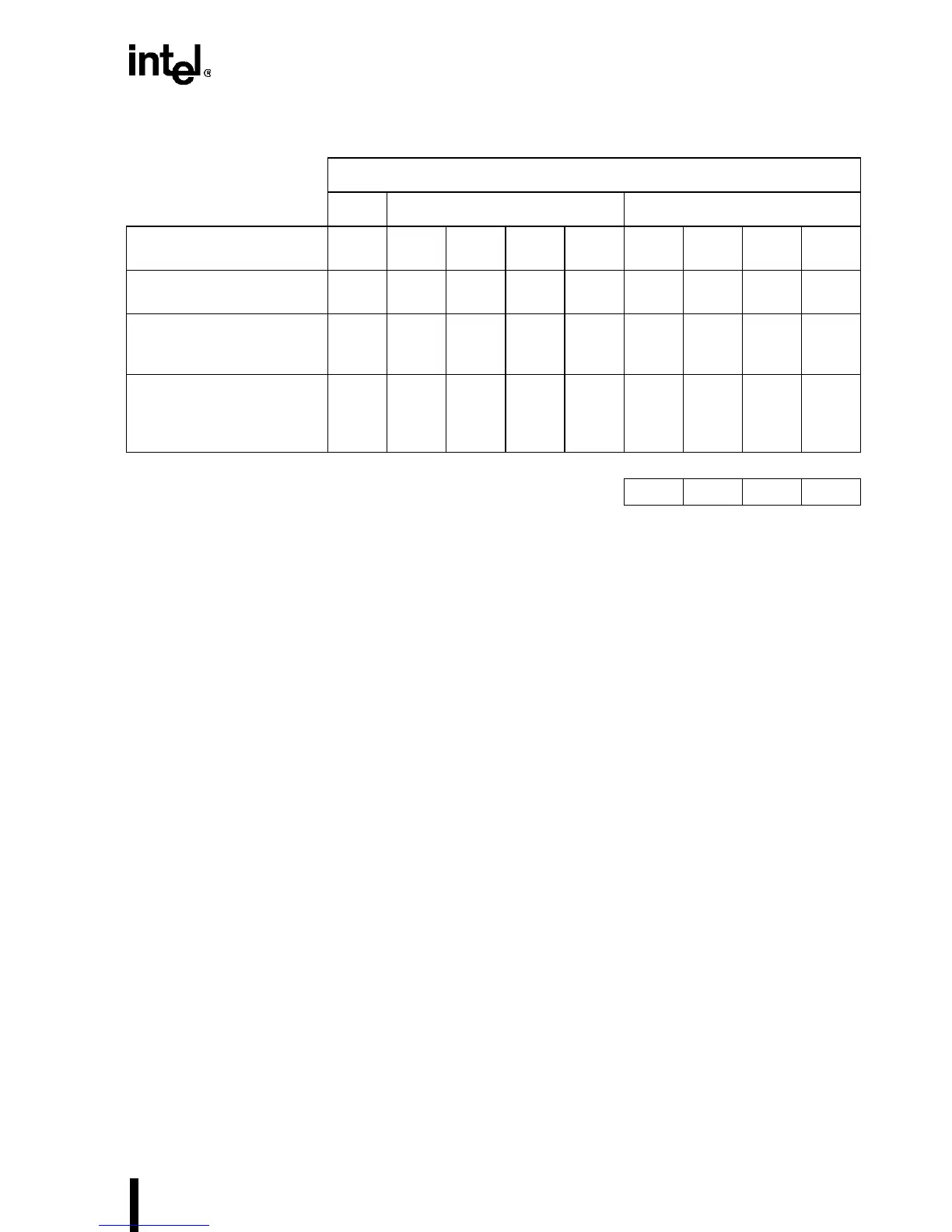

KEY:

b = byte transfer h = high-order portion 4-Byte Operand

w = 2-byte transfer l = low-order portion

3 = 3-byte transfer m = mid-order portion

d = 4-byte transfer

lb mlb mhb hb

↑ byte with

lowest address

↑byte with

highest address

Loading...

Loading...