3 - 53

3.4 Buffer Memory

3.4.1 Buffer memory assignment

3

SPECIFICATIONS

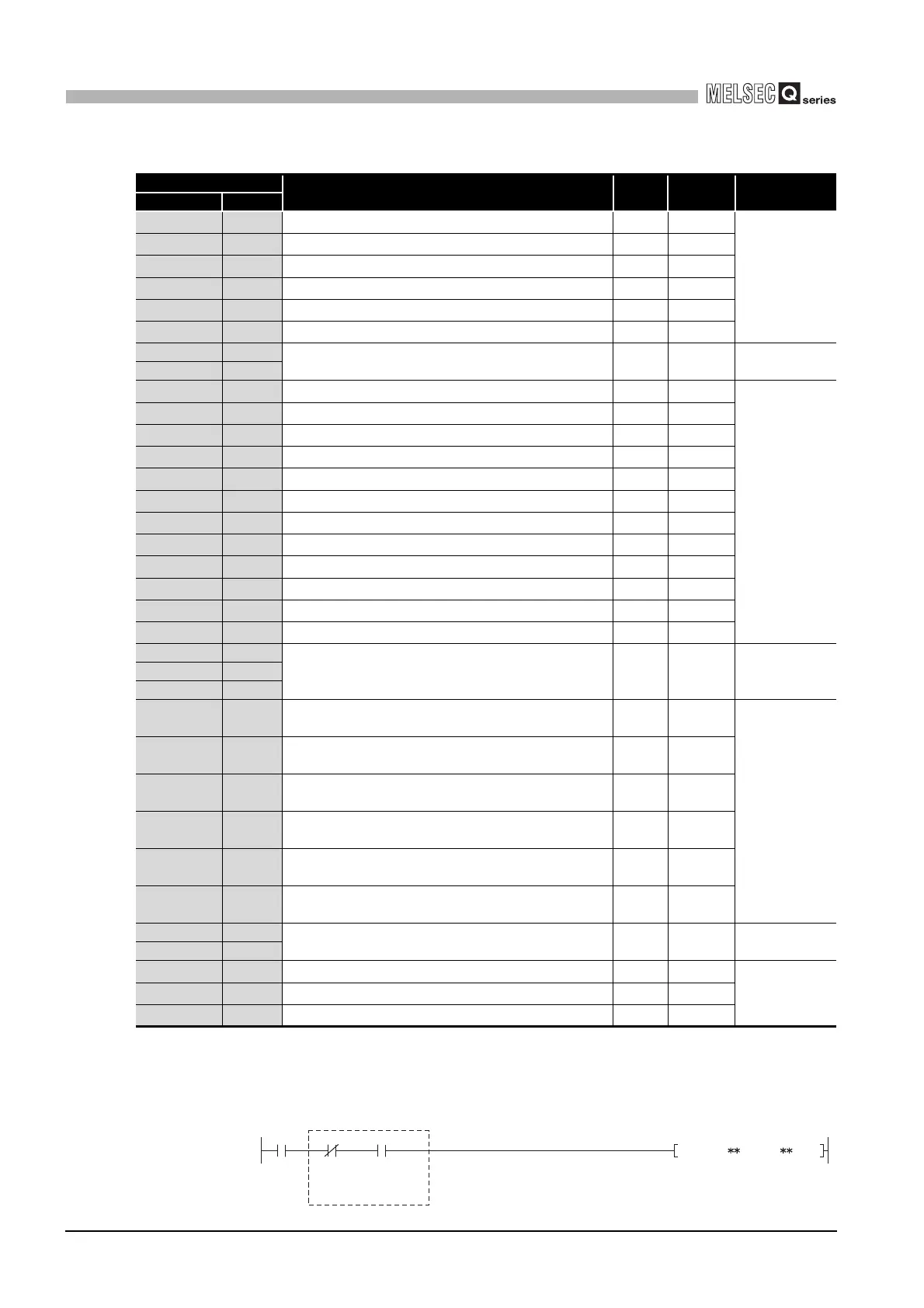

*1 Indicates whether reading from and writing to a sequence program are enabled.

R : Read enabled

W : Write enabled

*2 When writing data to the buffer memory, always use the interlock condition (buffer memory write con-

dition) of the following I/O signals

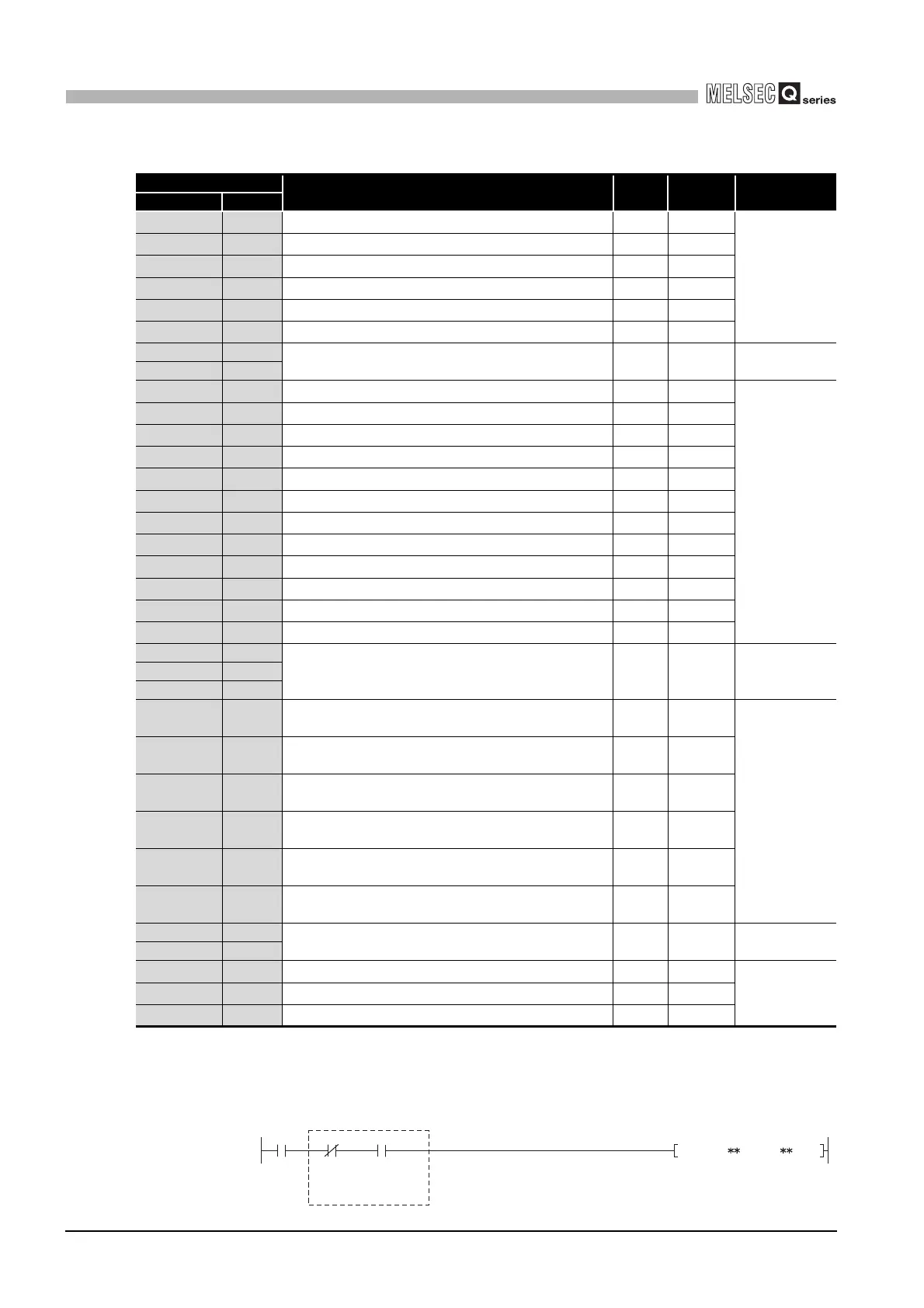

Table3.9 Buffer memory assignment of Q66AD-DG (4/5)

Address

Description Default

R/W

*1

Reference

Hexadecimal Decimal

76H 118 CH1 Rate alarm warning detection period 0

R/W

*2

Section 3.4.20

77H 119 CH2 Rate alarm warning detection period 0

R/W

*2

78H 120 CH3 Rate alarm warning detection period 0

R/W

*2

79H 121 CH4 Rate alarm warning detection period 0

R/W

*2

7AH 122 CH5 Rate alarm warning detection period 0

R/W

*2

7BH 123 CH6 Rate alarm warning detection period 0

R/W

*2

7CH 124

System area — — —

7DH 125

7EH 126 CH1 Rate alarm upper limit value 0

R/W

*2

Section 3.4.21

7FH 127 CH1 Rate alarm lower limit value 0

R/W

*2

80H 128 CH2 Rate alarm upper limit value 0

R/W

*2

81H 129 CH2 Rate alarm lower limit value 0

R/W

*2

82H 130 CH3 Rate alarm upper limit value 0

R/W

*2

83H 131 CH3 Rate alarm lower limit value 0

R/W

*2

84H 132 CH4 Rate alarm upper limit value 0

R/W

*2

85H 133 CH4 Rate alarm lower limit value 0

R/W

*2

86H 134 CH5 Rate alarm upper limit value 0

R/W

*2

87H 135 CH5 Rate alarm lower limit value 0

R/W

*2

88H 136 CH6 Rate alarm upper limit value 0

R/W

*2

89H 137 CH6 Rate alarm lower limit value 0

R/W

*2

8AH 138

System area — — —

to to

8DH 141

8EH 142

CH1 Input signal error detection setting value/CH1 Input

signal error detection lower limit setting value

50

R/W

*2

Section 3.4.22

8FH 143

CH2 Input signal error detection setting value/CH2 Input

signal error detection lower limit setting value

50

R/W

*2

90H 144

CH3 Input signal error detection setting value/CH3 Input

signal error detection lower limit setting value

50

R/W

*2

91H 145

CH4 Input signal error detection setting value/CH4 Input

signal error detection lower limit setting value

50

R/W

*2

92H 146

CH5 Input signal error detection setting value/CH5 Input

signal error detection lower limit setting value

50

R/W

*2

93H 147

CH6 Input signal error detection setting value/CH6 Input

signal error detection lower limit setting value

50

R/W

*2

94H 148

System area — — —

95H 149

96H 150 CH1 Input signal error detection upper limit setting value 50

R/W

*2

Section 3.4.2297H 151 CH2 Input signal error detection upper limit setting value 50

R/W

*2

98H 152 CH3 Input signal error detection upper limit setting value 50

R/W

*2

Writing

request

Y9 X9

Operating

condition

setting

completed

flag

Operating

condition

setting

request

Buffer memory writing condition

MOV

Loading...

Loading...