Pin Configuration 120 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

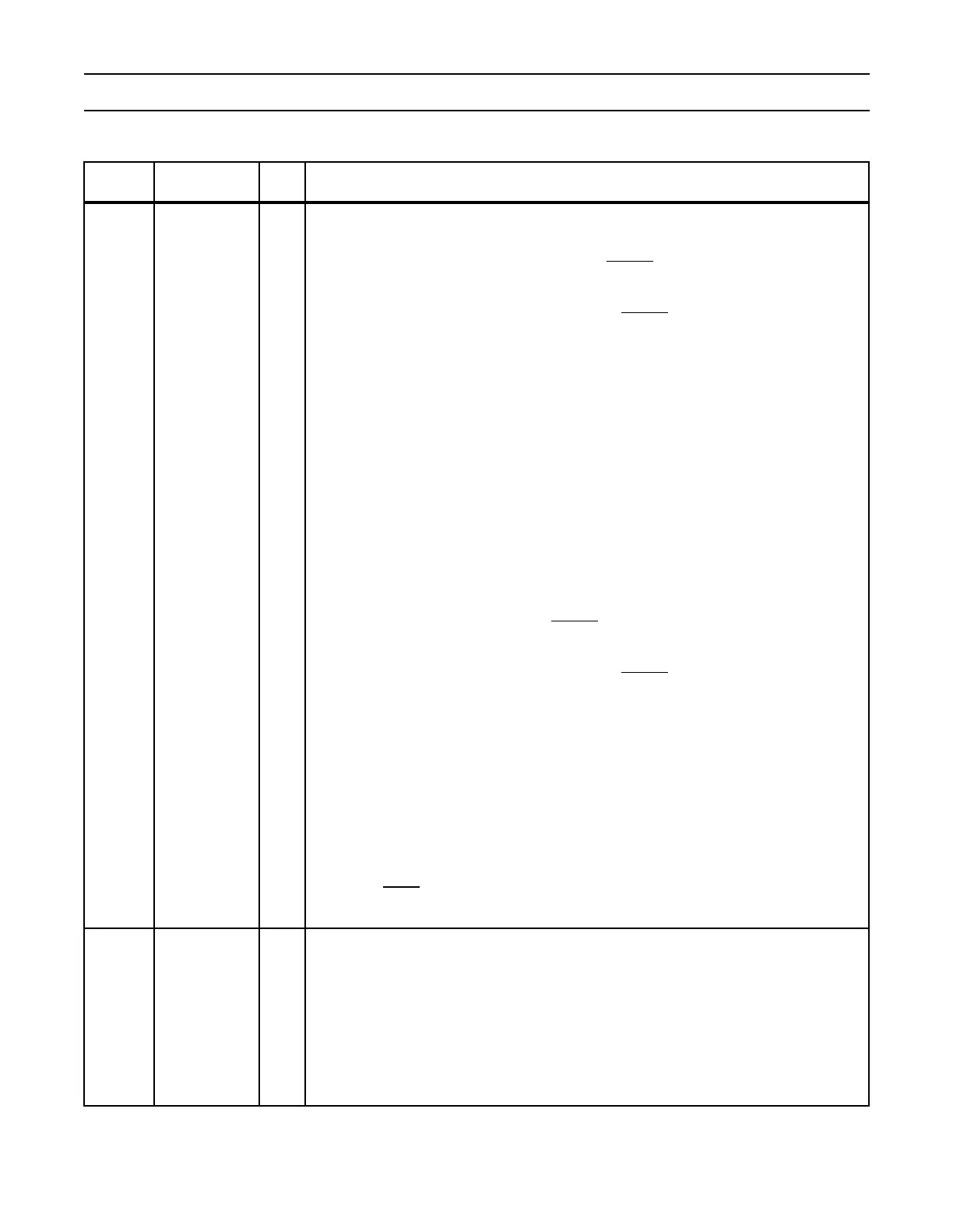

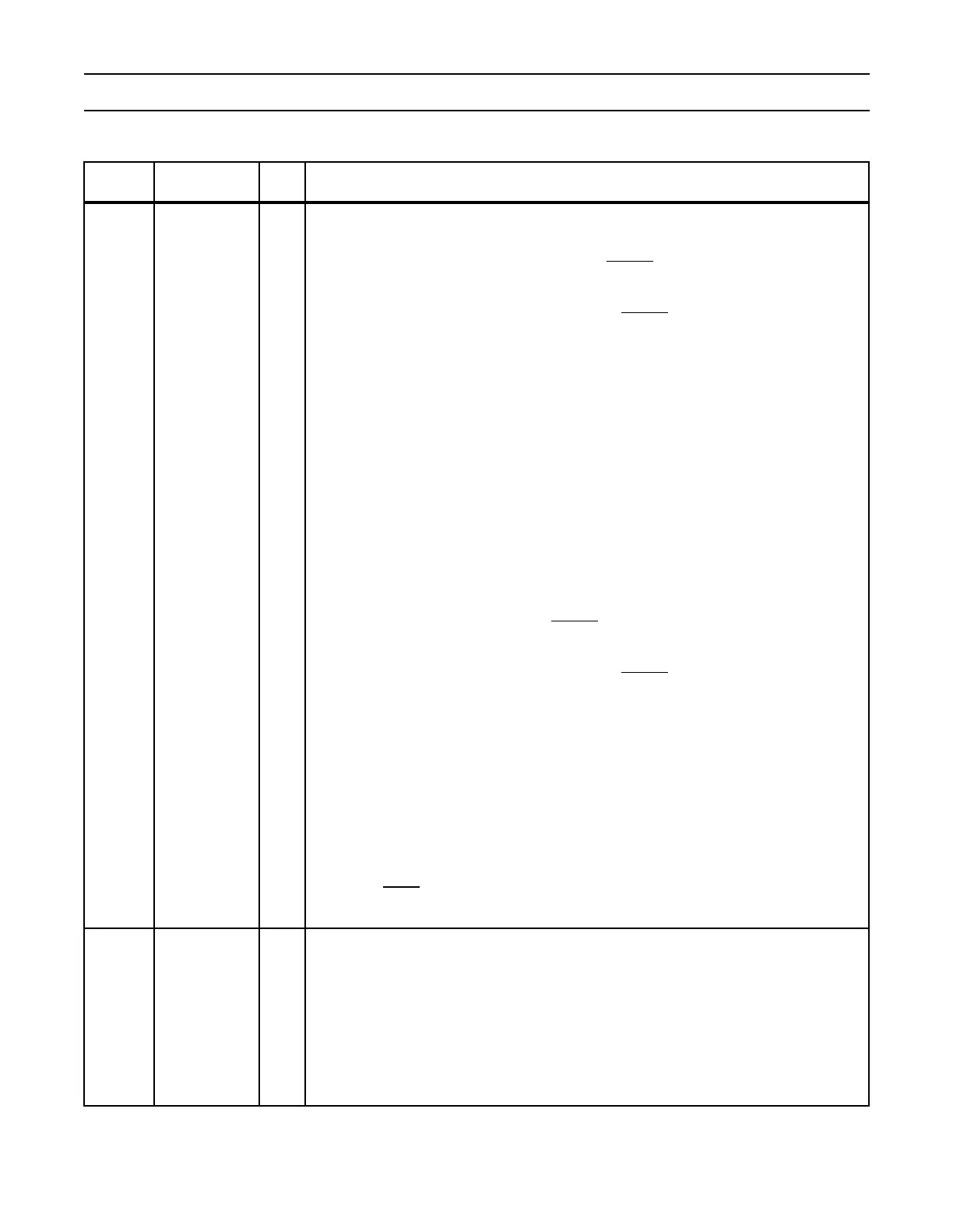

7O

P1.19 TRACEPKT3Trace Packet, bit 3. Standard I/O port with internal pull-up.

102

O P1.20 TRACESYNCTrace Synchronization. Standard I/O port with internal pull-up.

LOW on this pin while RESET is LOW enables pins P1.25:16 to

operate as a Trace port after reset.

Important: LOW on pin P1.20 while RESET

is LOW enables pins P1.25:16

to operate as a Trace port after reset.

95 O

P1.21 PIPESTAT0 Pipeline Status, bit 0. Standard I/O port with internal pull-up.

86 O

P1.22 PIPESTAT1 Pipeline Status, bit 1. Standard I/O port with internal pull-up.

82 O

P1.23 PIPESTAT2 Pipeline Status, bit 2. Standard I/O port with internal pull-up.

70 O

P1.24 TRACECLK Trace Clock. Standard I/O port with internal pull-up.

60 I

P1.25 EXTIN0 External Trigger Input. Standard I/O with internal pull-up.

52

I/O P1.26 RTCK Returned Test Clock output. Extra signal added to the JTAG

port. Assists debugger synchronization when processor

frequency varies. Bi-directional pin with internal pullup. LOW on

this pin while RESET

is LOW enables pins P1.31:26 to operate

as a Debug port after reset.

Important: LOW on pin P1.26 while RESET

is LOW enables pins P1.31:26

to operate as a Debug port after reset.

144 O

P1.27 TDO Test Data out for JTAG interface.

140 I

P1.28 TDI Test Data in for JTAG interface.

126 I

P1.29 TCK Test Clock for JTAG interface.

113 I

P1.30 TMS Test Mode Select for JTAG interface.

43 I

P1.31 TRST

Test Reset for JTAG interface.

P2.0

to

P2.31

98,105,106,10

8,109,114-

118,120,124,1

25,127,129-

134,136,137,1,

10-13,16-20

I/O

Port 2: Port 2 is a 32-bit bi-directional I/O port with individual direction controls for each bit.

The operation of port 2 pins depends upon the pin function selected via the Pin Connect

Block.

Note: All Port 2 pins excluding those that can be used as A/D inputs (P2.30 and P2.31)

are functionally 5V tolerant. Port 2 pin configured to perform an input function will use built-

in pull-up resistor to set the default input level to high. If the A/D converter is not used at all,

pins associated with A/D inputs can be used as 5V tolerant digital IO pins. See "A/D

Converter" chapter for A/D input pin voltage considerations.

Table 56: Pin description for LPC2292/2294

Pin

Name

LQFP144

Pin #

Type Description

Loading...

Loading...