Introduction 24 May 03, 2004

Philips Semiconductors Preliminary User Manual

LPC2119/2129/2194/2292/2294ARM-based Microcontroller

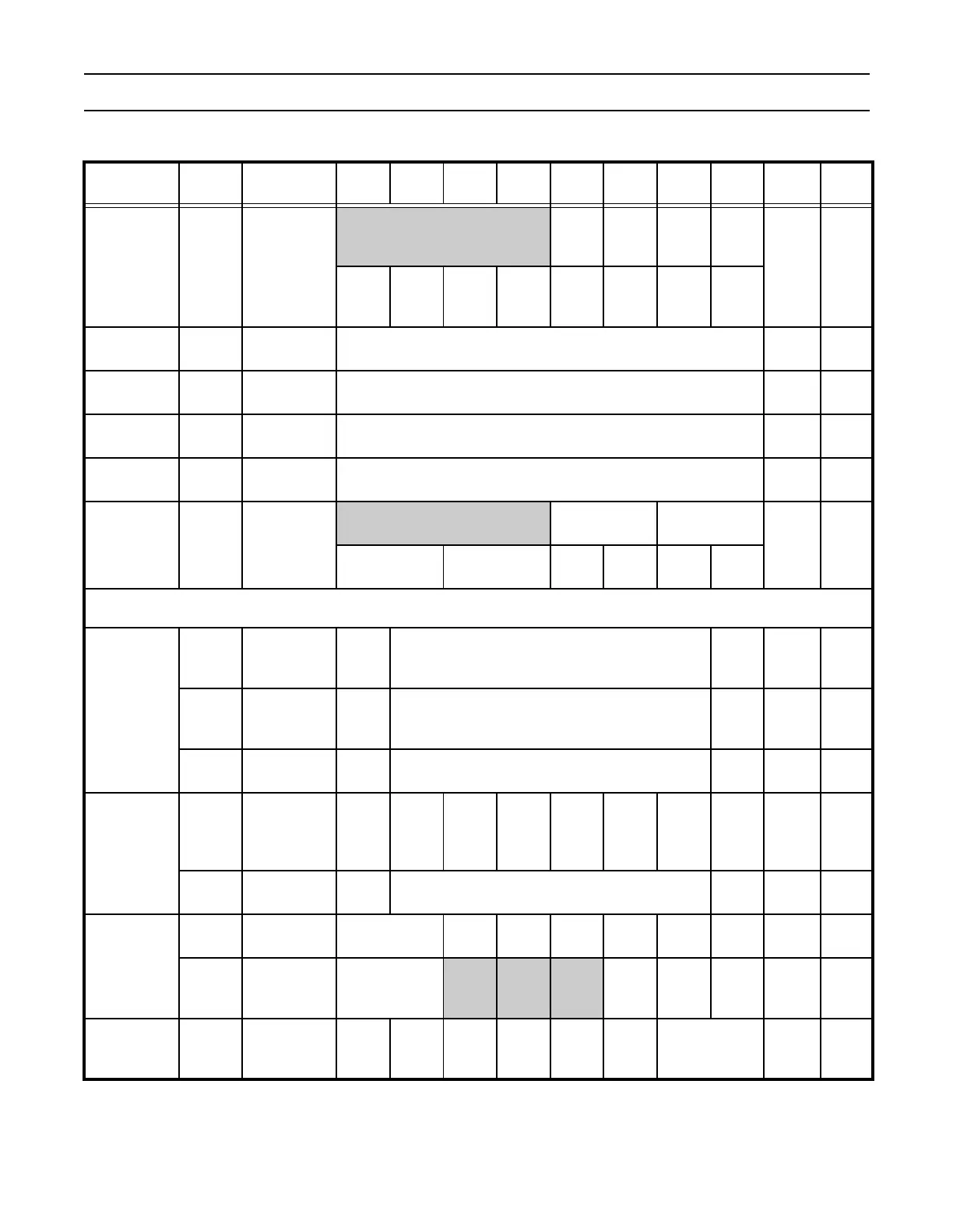

0xE0008028 T1CCR

T1 Capture

Control

Register

4 reserved (-) bits

Int. on

Cpt.3

Int. on

Cpt.3

falling

Int. on

Cpt.3

rising

Int. on

Cpt.2

R/W 0

Int. on

Cpt.2

falling

Int. on

Cpt.2

rising

Int. on

Cpt.1

Int. on

Cpt.1

falling

Int. on

Cpt.1

rising

Int. on

Cpt.0

Int. on

Cpt.0

falling

Int. on

Cpt.0

rising

0xE000802C T1CR0

T1 Capture

Register 0

32 bit data RO 0

0xE0008030 T1CR1

T1 Capture

Register 1

32 bit data RO 0

0xE0008034 T1CR2

T1 Capture

Register 2

32 bit data RO 0

0xE0008038 T1CR3

T1 Capture

Register 3

32 bit data RO 0

0xE000803C T1EMR

T1 External

Match

Register

4 reserved (-) bits

External Match

Control 3

External Match

Control 2

R/W 0

External Match

Control 1

External Match

Control 0

Ext.

Mtch.3

Ext.

Mtch2.

Ext.

Mtch.1

Ext.

Mtch.0

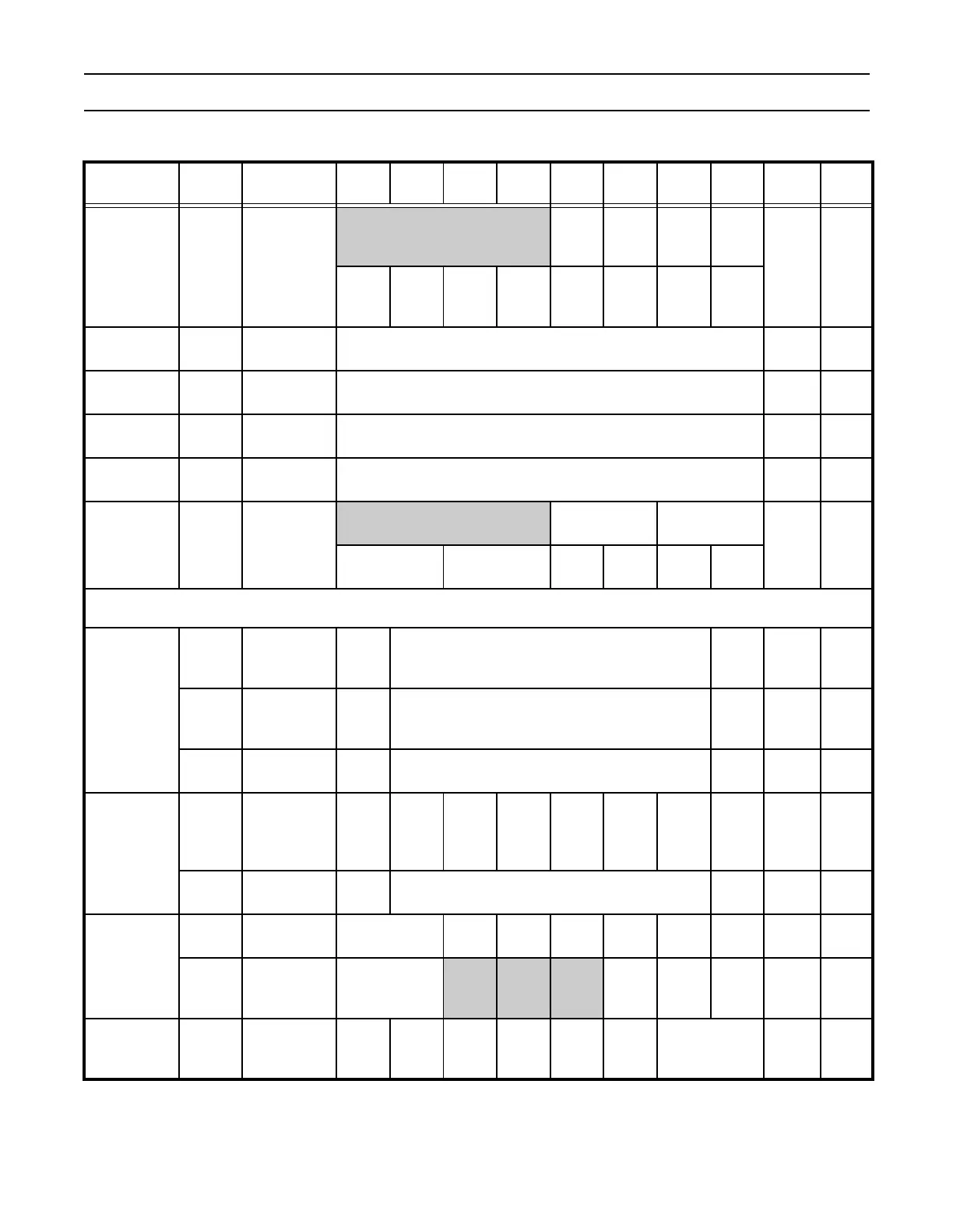

UART0

0xE000C000

U0RBR

(DLAB=0)

U0 Receiver

Buffer

Register

8 bit data RO

un-

defined

U0THR

(DLAB=0)

U0 Transmit

Holding

Register

8 bit data WO NA

U0DLL

(DLAB=1)

U0 Divisor

Latch LSB

8 bit data R/W 0x01

0xE000C004

U0IER

(DLAB=0)

U0 Interrupt

Enable

Register

00000

En. Rx

Line

Status

Int.

Enable

THRE

Int.

En. Rx

Data

Av.Int.

R/W 0

U0DLM

(DLAB=1)

U0 Divisor

Latch MSB

8 bit data R/W 0

0xE000C008

U0IIR

U0 Interrupt

ID Register

FIFOs Enabled 0 0 IIR3 IIR2 IIR1 IIR0 RO 0x01

U0FCR

U0 FIFO

Control

Register

Rx Trigger

- - -

U0 Tx

FIFO

Reset

U0 Rx

FIFO

Reset

U0

FIFO

Enable

WO 0

0xE000C00C U0LCR

U0 Line

Control

Register

DLAB

Set

Break

Stick

Parity

Even

Parity

Select

Parity

Enable

Nm. of

Stop

Bits

Word Length

Select

R/W 0

Table 2: LPC2119/2129/2194/2292/2294 Registers

Address

Offset

Name Description MSB LSB Access

Reset

Value

Loading...

Loading...