RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1164

Dec 10, 2015

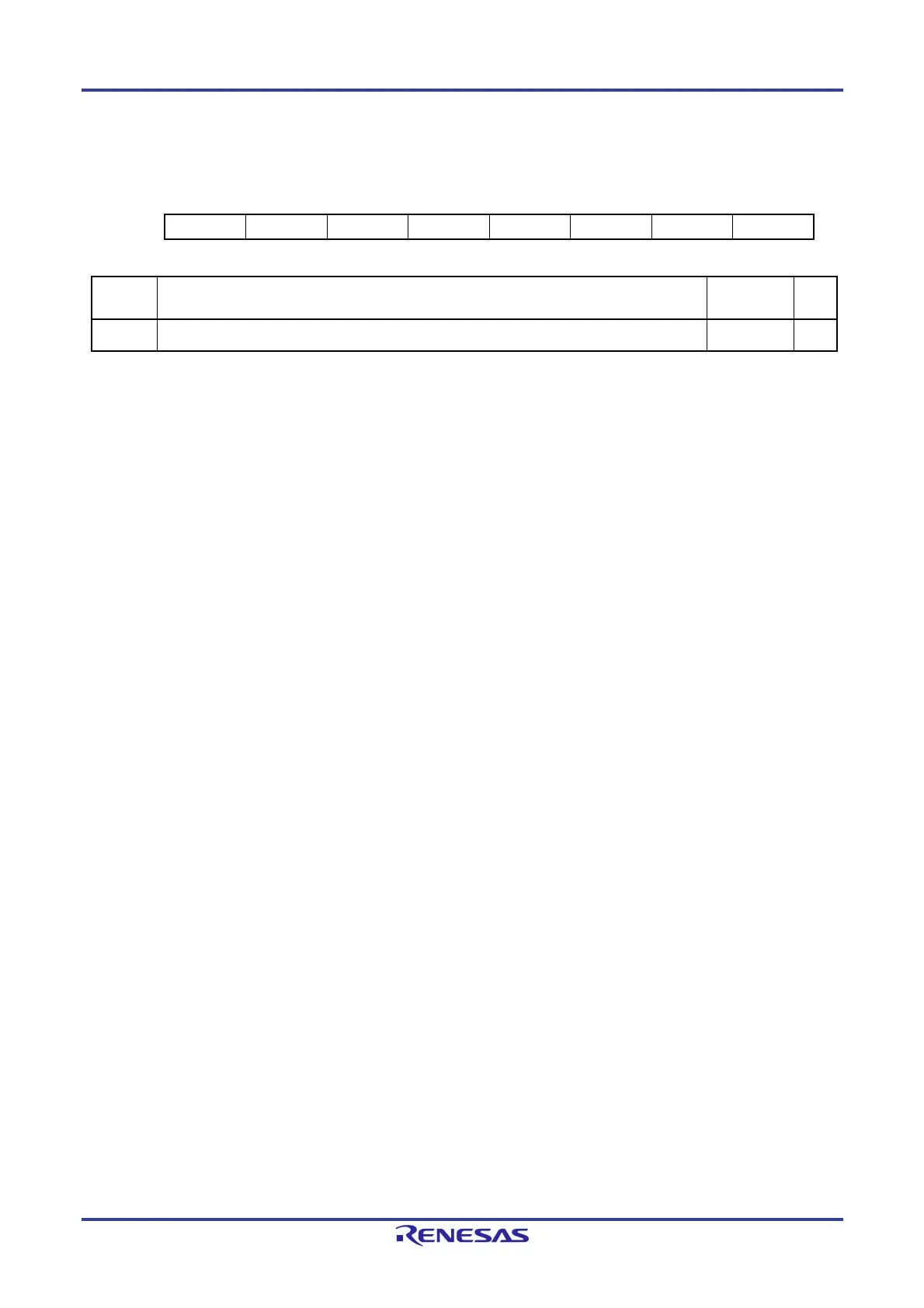

(23) LIN/UART Data Buffer m Register (LDBnm) (m = 1 to 8)

Address: LDBn1 F06D8H, LDBn2 F06D9H, LDBn3 F06DAH, LDBn4 F06DBH, LDBn5 F06DCH, LDBn6 F06DDH, LDBn7 F06DEH, LDBn8 F06DFH

7 6 5 4 3 2 1 0

Value after reset:

0 0 0 0 0 0 0 0

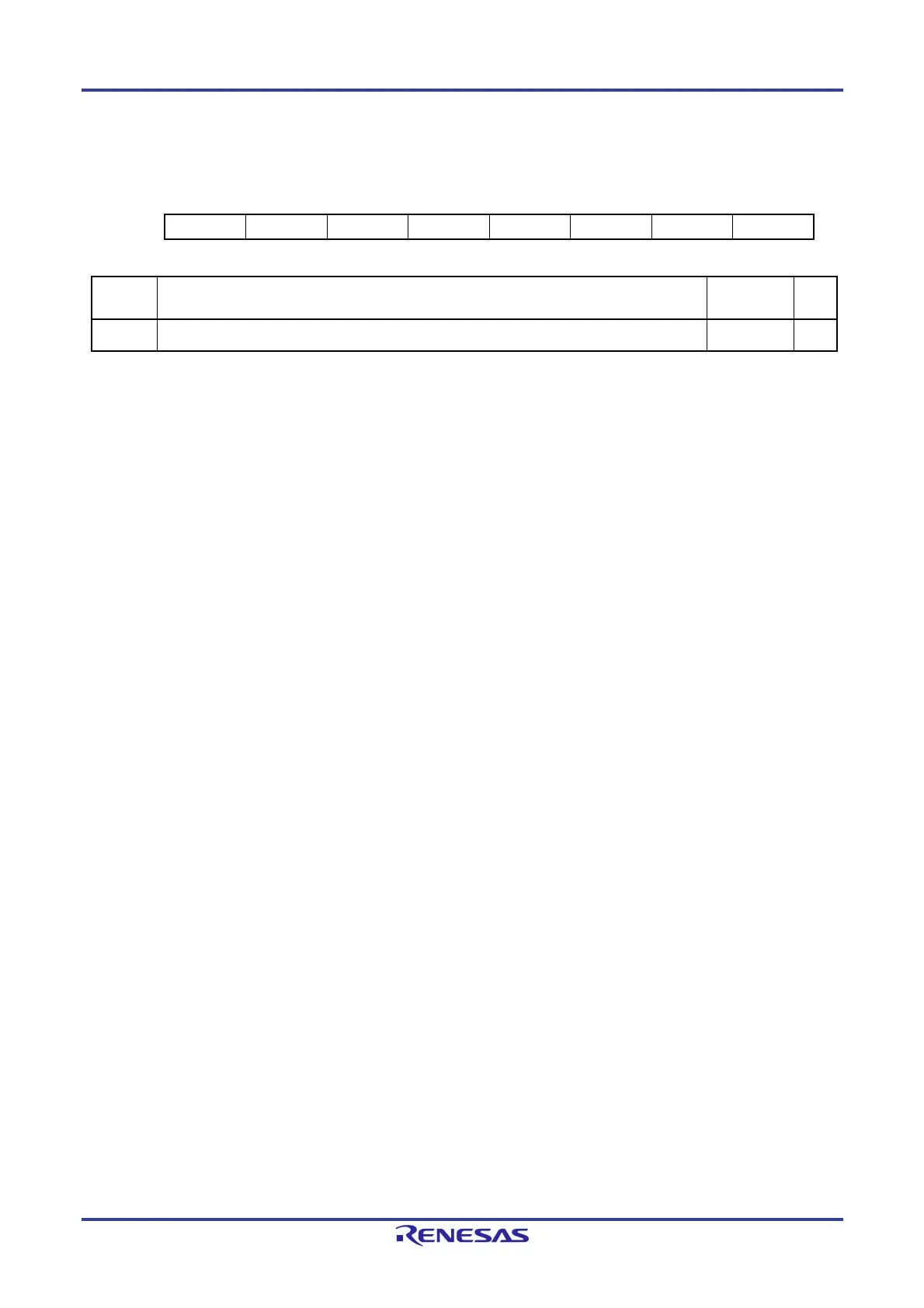

Bit Function

Setting

Range

R/W

7 to 0 Sets the data to be transmitted or allows the received data to be read. 00H to FFH R/W

For response transmission:

These registers set the data to be transmitted in the response field.

Set these registers when the RTS bit is 0 (response reception/transmission is halted).

For response reception:

These registers hold the data received in the response field.

The received data is overwritten. If an error is detected, the data prior to reception interruption is stored in the register.

Do not read these registers when the RTS bit is 1 (response transmission/reception is started)

In LIN self-test mode, this register operates as follows:

Write the value to be transmitted before communication. The reversed value of the value received can be read from the

register after frame transmission/reception is completed (after loopback).

For details of LIN self-test mode, refer to 17.6 LIN Self-Test Mode.

Loading...

Loading...