RL78/F13, F14 CHAPTER 4 PORT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 324

Dec 10, 2015

4.3.5 Port output mode registers (POM1, POM6, POM7, POM12)

These registers set the output mode of P10 to P17, P60 to P63, P70 to P72, and P120 in 1-bit units.

N-ch open-drain output (EVDD tolerance) mode can be selected for the SDA00, SDA01, SDA10, and SDA11 pins

during serial communication with an external device of the different potential or during simplified IIC communication

with an external device of the same potential, and it can be also selected for the SDAA0 and SCLA0 pins during IIC

communication.

These registers can be set by a 1-bit or 8-bit memory manipulation instruction.

Reset signal generation clears these registers to 00H.

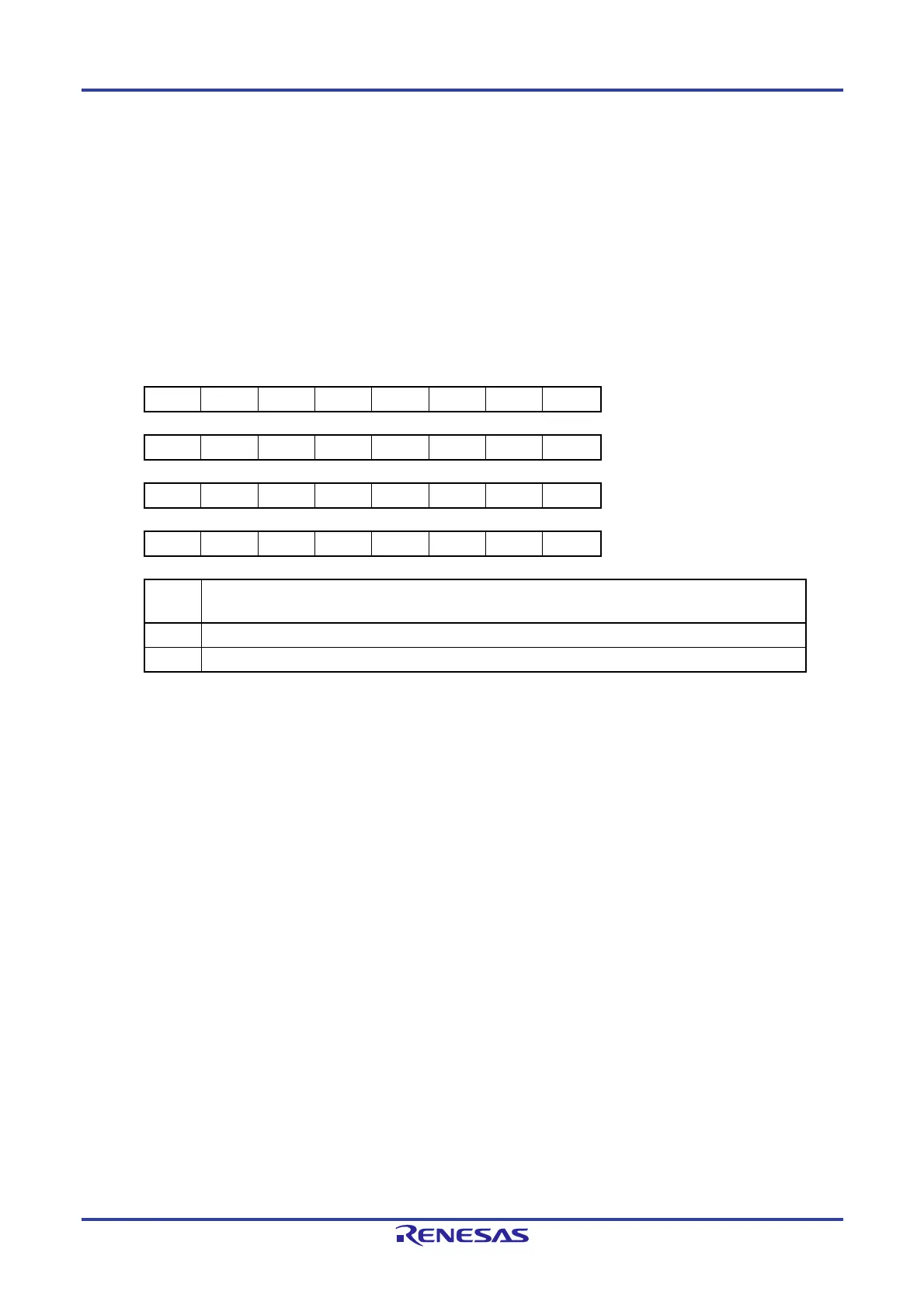

Figure 4-78. Format of Port Output Mode Register (100-pin products)

Symbol 7 6 5 4 3 2 1 0 Address After reset R/W

POM1 POM17 POM16 POM15 POM14 POM13 POM12 POM11 POM10

F0051H 00H R/W

POM6 0 0 0 0 POM63 POM62 POM61 POM60

F0056H 00H R/W

POM7 0 0 0 0 0 POM72 POM71 POM70

F0057H 00H R/W

POM12 0 0 0 0 0 0 0 POM120

F005CH 00H R/W

POMmn

Pmn pin output mode selection

(m = 1, 6, 7, 12; n = 0 to 7)

0 Normal output mode

1 N-ch open-drain output (EVDD tolerance) mode

Cautions 1. The on-chip pull-up resistor cannot be used when POMmn is set to 1.

2. Be sure to set bits for pins that are not present to their initial values.

Loading...

Loading...