RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1446

Dec 10, 2015

19.2.15 High-speed DTC Control Register m (HDTCCR0/1) (m = 0, 1)

The HDTCCRm register is used to control the high-speed DTC transfer operating mode.

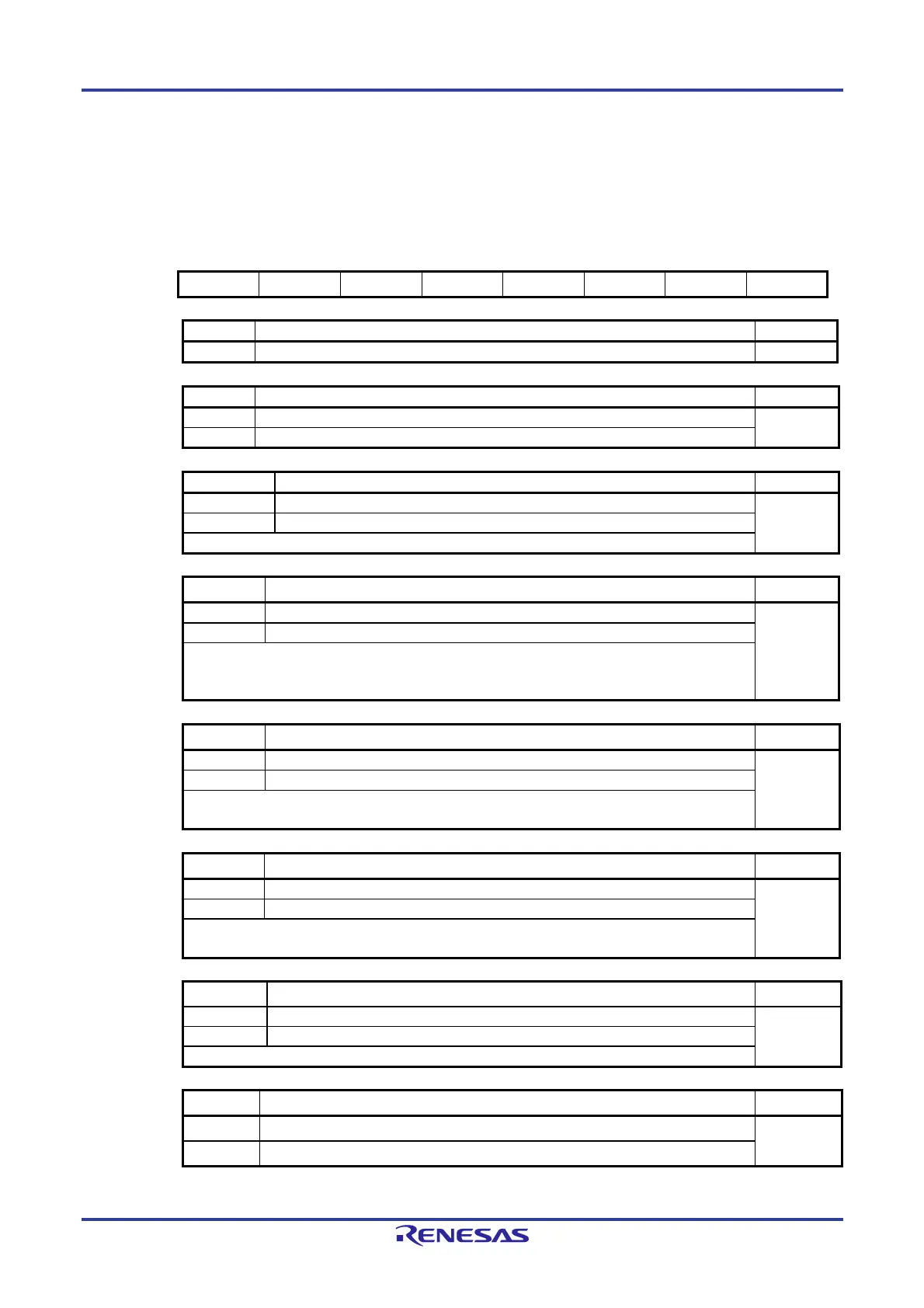

Figure 19-15. Format of High-speed DTC Control Register m (HDTCCRm)

Address: F02D0H (HDTCCR0), F02D8H (HDTCCR1) After reset: 00H

Symbol 7 <6> <5> <4> <3> <2> <1> <0>

HDTCCRm 0 HSZm HRPTINTm HCHNEm HDAMODm HSAMODm HRPTSELm HMODEm

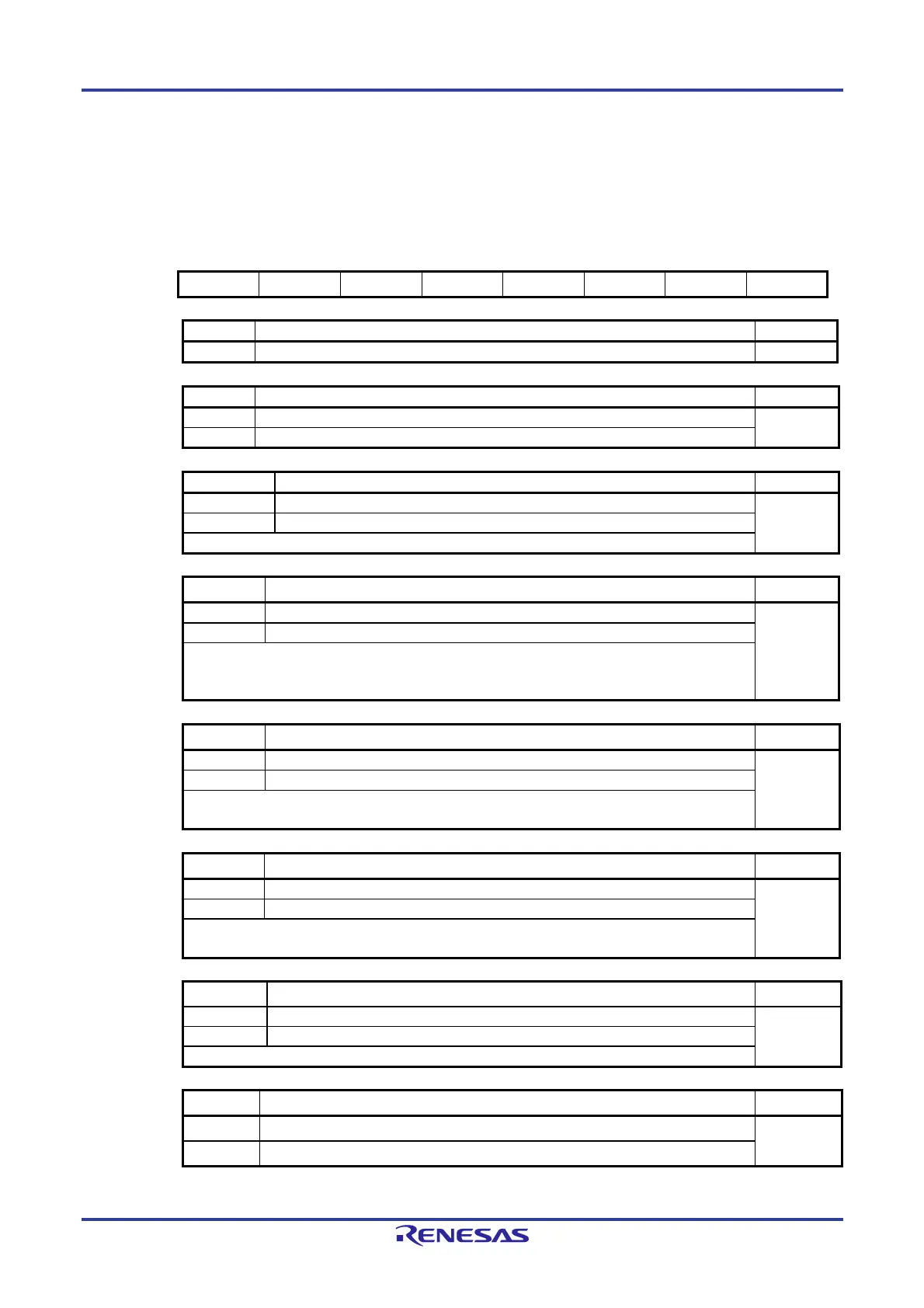

Bit 7 Reserved R/W

0 Set to 0. R/W

HSZm Data size selection R/W

0 8 bits R/W

1 16 bits

HRPTINTm Enabling/disabling repeat mode interrupts R/W

0 Interrupt generation disabled R/W

1 Interrupt generation enabled

The setting of the HRPTINTm bit is invalid when the HMODEm bit is 0 (normal mode).

HCHNEm Enabling/disabling chain transfers

R/W

0 Chain transfers disabled

R/W

1 Chain transfers enabled

Set the CHNE bit in the DTCCR23 register to 0 (chain transfers disabled).

Set the HCHNEm bit to 0 (chain transfers disabled) when the activation source number is set to the

maximum value by the SELHSm register.

HDAMODm Transfer destination address control

R/W

0 Fixed

R/W

1 Incremented

The setting of the HDAMODm bit is invalid when the HMODEm bit is 1 (repeat mode) and the

HRPTSELm bit is 0 (transfer destination is the repeat area).

HSAMODm Transfer source address control

R/W

0 Fixed

R/W

1 Incremented

The setting of the HSAMODm bit is invalid when the HMODEm bit is 1 (repeat mode) and the

HRPTSELm bit is 1 (transfer source is the repeat area).

HRPTSELm Repeat area selection

R/W

0 Transfer destination is the repeat area

R/W

1 Transfer source is the repeat area

The setting of the HRPTSELm bit is invalid when the HMODEm bit is 0 (normal mode).

HMODEm Transfer mode selection R/W

0 Normal mode R/W

1 Repeat mode

Caution Do not access the HDTCCRm register using a high-speed DTC transfer.

Loading...

Loading...