RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 390

Dec 10, 2015

5.3.12 Clock Select Register (CKSEL)

This register is used to select the CPU clock (f

SUB/fIL) and the clocks for the timer RJ, the timer RD, and clock

output/buzzer output. Together with the CMC register, the SELLOSC bit is used to set the operation mode of the

subsystem clock. For details, see Figure 5-3 Format of Clock Operation Mode Control Register (CMC).

Set the CKSEL register by a 1-bit or 8-bit memory manipulation instruction.

Writing to the CKSEL register is disabled when the GCSC bit of the IAWCTL register is set to 1.

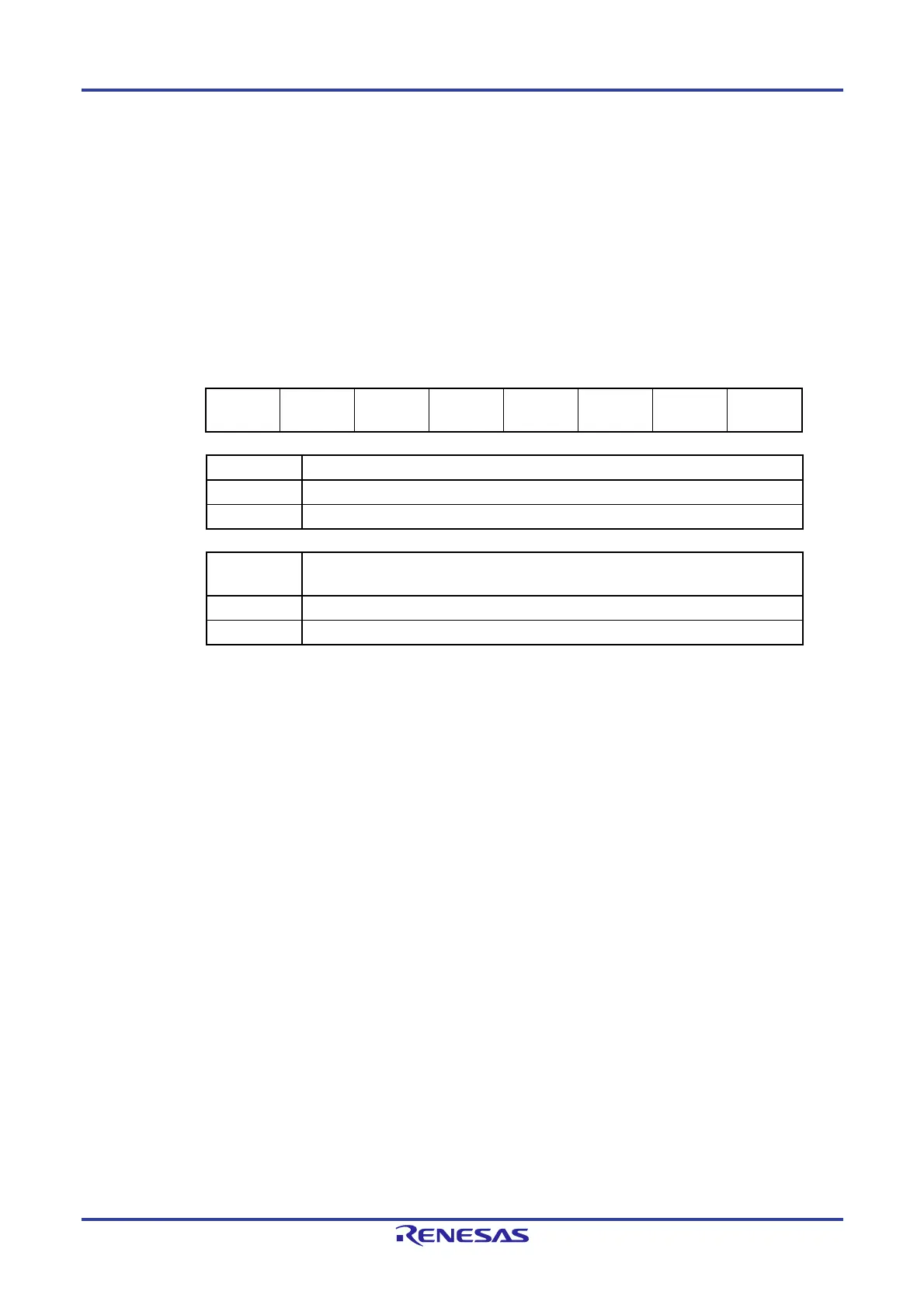

Figure 5-19. Format of Clock Select Register (CKSEL)

Address: F02C4H After reset: 00H R/W

Symbol 7 6 5 4 3 <2> 1 <0>

CKSEL 0 0

0 0

0

TRD_

CKSEL

0

SELLOSC

Note 5, 6, 7

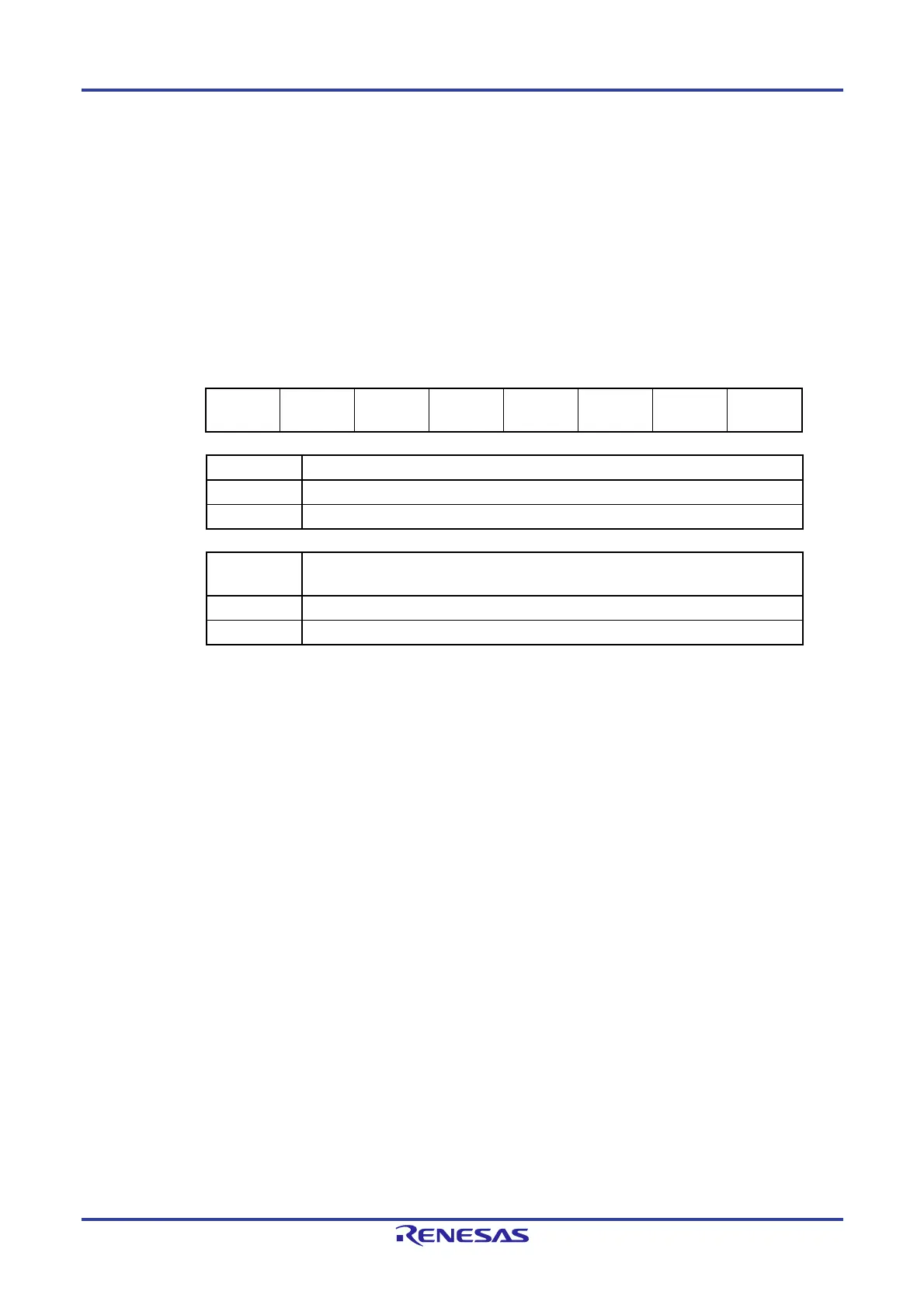

TRD_CKSEL Control of TDR clock selection

0 Selects fCLK or fMP

Note 1

1 Selects fSL

Note 2

SELLOSC

Note 5, 6, 7

Control of subsystem/low-speed on-chip oscillator selection clock (f

SL) selection

0 Selects fSUB

Note 3

and stopping the low-speed on-chip oscillator

1 Selects fIL

Note 4

and running the low-speed on-chip oscillator

Notes 1. When FRQSEL4 = 1 in the user option byte (000C2H/020C2H) and PLLDIV1 = 1 (f

PLL 32

MHz) in the PLLCTL register, set the TRD_CKSEL bit to 0.

When FRQSEL4 = 1 in the user option byte (000C2H/020C2H) or PLLDIV1 = 1 (f

PLL 32

MHz) in the PLLCTL register, the timer RD clock becomes fMP.

2. When f

SL is selected as the timer RD clock, fSL should be selected as the CPU clock (set the

CSS bit in the CKC register to 1) before setting the TRD0EN bit in the peripheral enable

register 1 (PER1) to 1.

3. When setting f

SUB as the CPU/peripheral hardware clock, first set the SELLOSC bit in the

CKSEL register to 0 and then set the CSS bit in the CKC register to 1 .

4. When setting f

IL as the CPU/peripheral hardware clock, first set the SELLOSC bit in the

CKSEL register to 1 and then set the CSS bit in the CKC register to 1.

5. When the SELLOSC bit is set to 1, the low-speed on-chip oscillator operates. To stop the low-

speed on-chip oscillator, set the WUTMMCK0 bit in the OSMC register to 0 and the SELLOSC

bit to 0.

6. The 20-, 30-, and 32-pin products do not have a subsystem clock (f

SUB). If the low-speed on-

chip oscillator is selected as the source of the clock signal for the CPU/peripheral hardware

clock (fCLK) or for a peripheral function, set the SELLOSC bit to 1.

7. When the SELLOSC bit is set to 1, the subsystem clock (f

SUB) cannot be supplied to the input

clock (f

RTC) of the real-time clock.

Loading...

Loading...