RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1443

Dec 10, 2015

19.2.10 DTC Transfer Count Reload Register j (DTRLDj) (j = 0 to 23)

This register is used to set the initial value of the transfer count register in repeat mode. Since the value of this register

is reloaded to the DTCCT register in repeat mode, set the same value as the initial value of the DTCCT register.

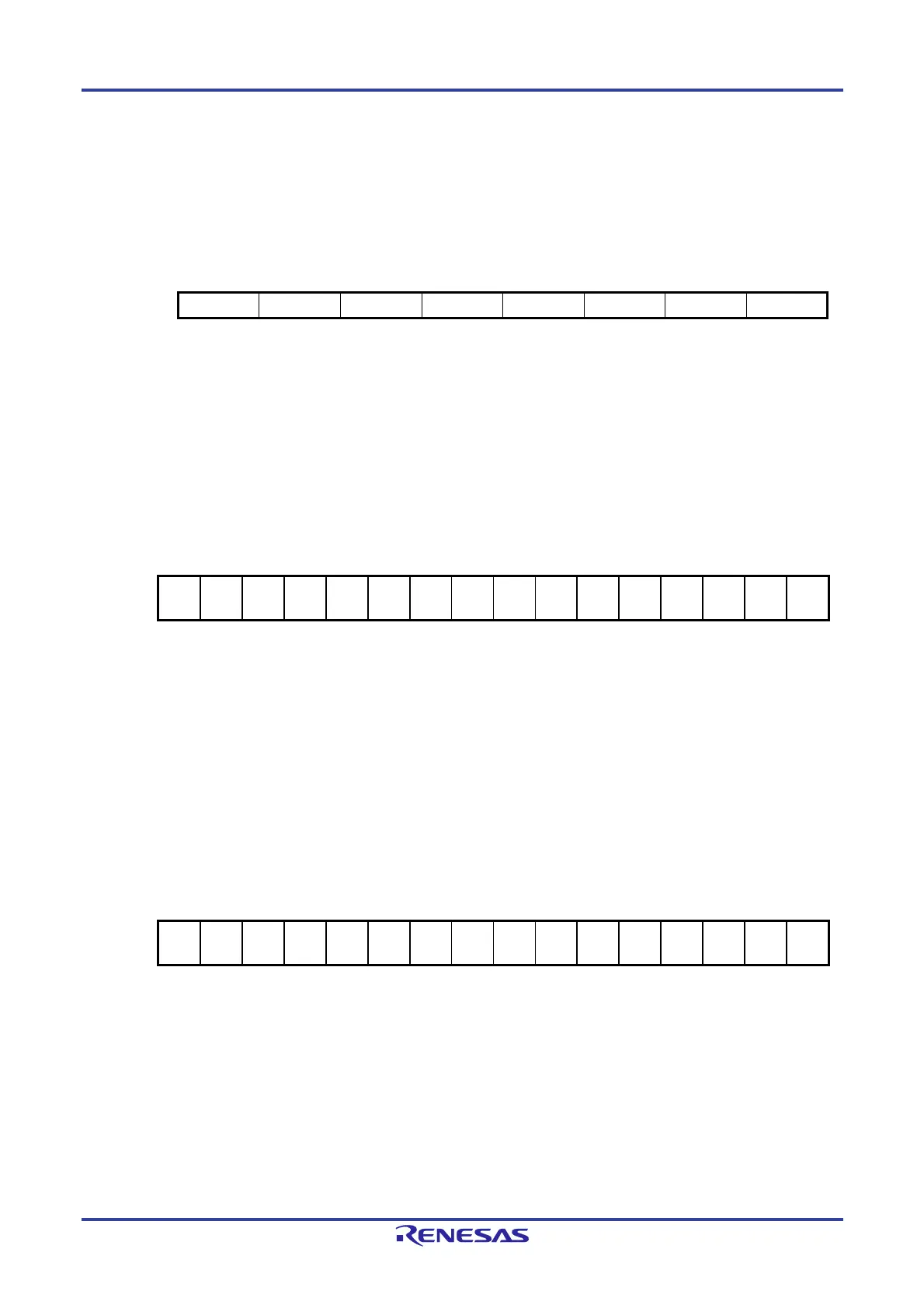

Figure 19-10. Format of DTC Transfer Count Reload Register j (DTRLDj)

Address: Refer to 19.2.2 DTC Control Data Allocation. After reset: Undefined

Symbol 7 6 5 4 3 2 1 0

DTRLDj DTRLDj7 DTRLDj6 DTRLDj5 DTRLDj4 DTRLDj3 DTRLDj2 DTRLDj1 DTRLDj0

Caution Do not access the DTRLDj register using a DTC transfer.

19.2.11 DTC Source Address Register j (DTSARj) (j = 0 to 23)

This register is used to specify the transfer source address for data transfer.

When the SZ bit in the DTCCRj register is set to 1 (16-bit transfer), the lowest bit is ignored and the address is handled

as an even address.

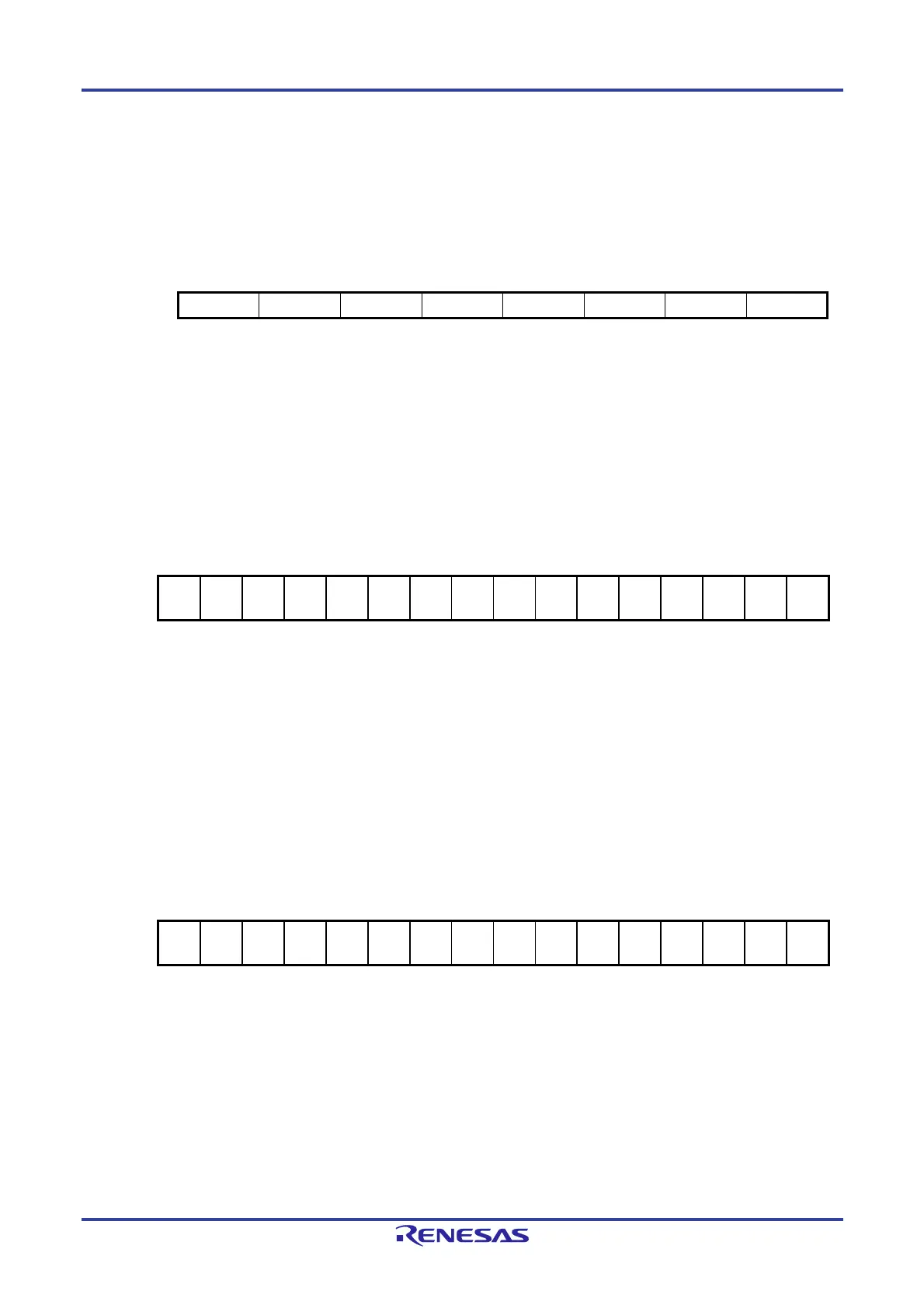

Figure 19-11. Format of DTC Source Address Register j (DTSARj)

Address: Refer to 19.2.2 DTC Control Data Allocation. After reset: Undefined

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DTSARj

DTS

ARj15

DTS

ARj14

DTS

ARj13

DTS

ARj12

DTS

ARj11

DTS

ARj10

DTS

ARj9

DTS

ARj8

DTS

ARj7

DTS

ARj6

DTS

ARj5

DTS

ARj4

DTS

ARj3

DTS

ARj2

DTS

ARj1

DTS

ARj0

Cautions 1. Do not set the general-purpose register (FFEE0H to FFEFFH) space to the transfer source

address.

2. Do not access the DTSARj register using a DTC transfer.

19.2.12 DTC Destination Address Register j (DTDARj) (j = 0 to 23)

This register is used to specify the transfer destination address for data transfer.

When the SZ bit in the DTCCRj register is set to 1 (16-bit transfer), the lowest bit is ignored and the address is handled

as an even address.

Figure 19-12. Format of DTC Destination Address Register j (DTDARj)

Address: Refer to 19.2.2 DTC Control Data Allocation. After reset: Undefined

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DTDARj

DTD

ARj15

DTD

ARj14

DTD

ARj13

DTD

ARj12

DTD

ARj11

DTD

ARj10

DTD

ARj9

DTD

ARj8

DTD

ARj7

DTD

ARj6

DTD

ARj5

DTD

ARj4

DTD

ARj3

DTD

ARj2

DTD

ARj1

DTD

ARj0

Cautions 1. Do not set the general-purpose register (FFEE0H to FFEFFH) space to the transfer source

address.

2. Do not access the DTDARj register using a DTC transfer.

Loading...

Loading...