RL78/F13, F14 CHAPTER 10 CLOCK OUTPUT/BUZZER OUTPUT CONTROLLER

R01UH0368EJ0210 Rev.2.10 690

Dec 10, 2015

4. The high-speed on-chip oscillator clock (fIH) and the high-speed system clock (fMX) can be selected

as the main system clock (fMAIN) by the setting of the MCM0 bit (bit 4 of the system clock control

register (CKC)). For details, refer to CHAPTER 5 CLOCK GENERATOR.

5. The subsystem clock (f

SUB) and the low-speed on-chip oscillator clock (fIL) can be selected as the

sub/low-speed on-chip oscillator select clock by the setting of the SELLOSC bit (bit 0 of the clock

select register (CKSEL)). For details, refer to CHAPTER 5 CLOCK GENERATOR.

10.3.2 Clock Select Register (CKSEL)

This register is used to select the CPU clock (fSUB/fIL) the clocks for the timer RJ, timer RD, and clock output/buzzer

output. Together with the CMC register, the SELLOSC bit is used to set the operation mode of the subsystem clock.

For details, see Figure 5-3 Format of Clock Operation Mode Control Register (CMC).

Set the CKSEL register by a 1-bit or 8-bit memory manipulation instruction.

Writing to the CKSEL register is disabled when the GCSC bit of the IAWCTL register is set to 1.

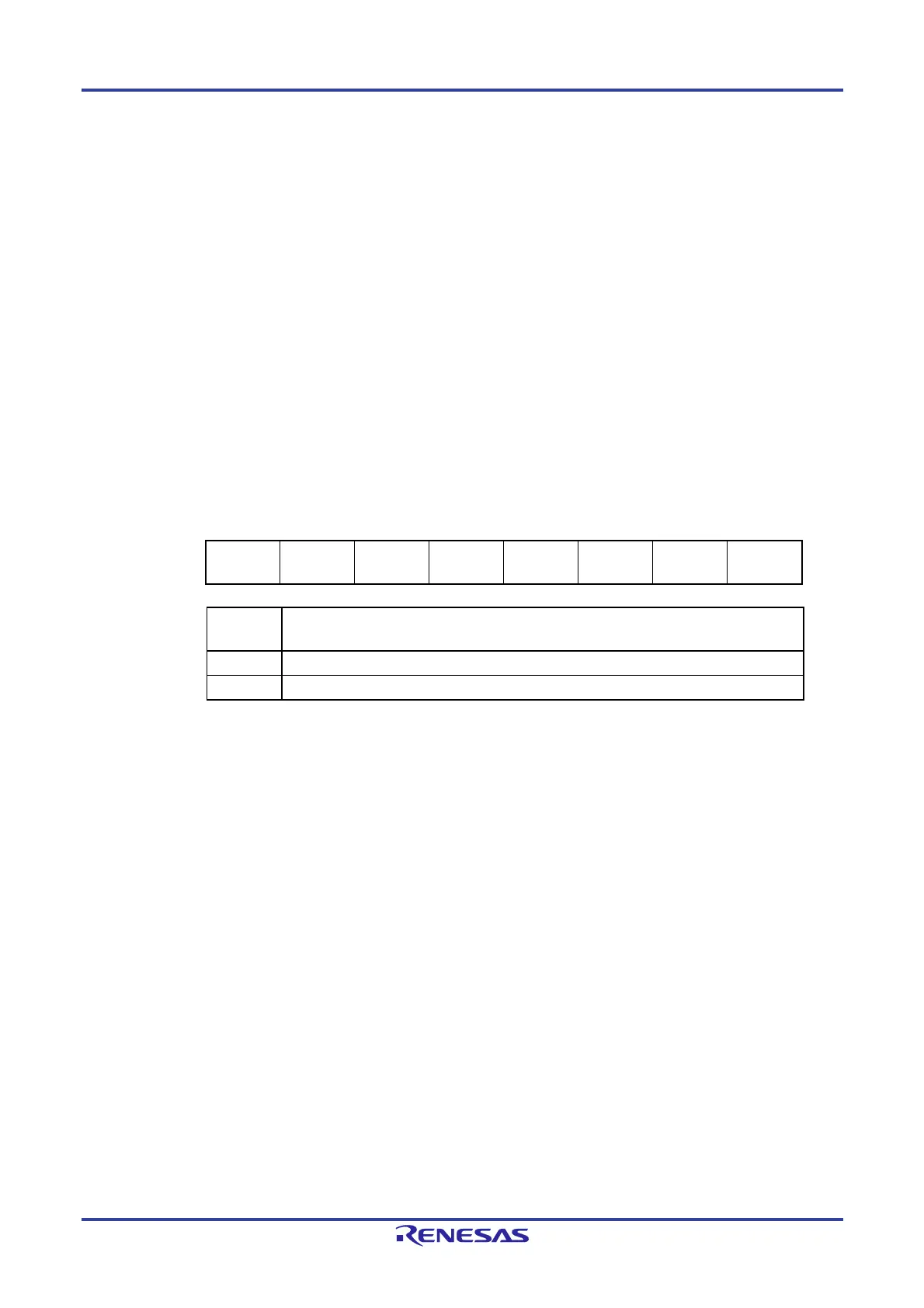

Figure 10-3. Format of Clock Select Register (CKSEL)

Address: F02C4H After reset: 00H R/W

Symbol 7 6 5 4 3 <2> 1 <0>

CKSEL 0 0

0 0

0

TRD_CKS

EL

0

SELLOSC

Notes 3, 4

SELLOSC

Notes 3, 4

Control of sub/low-speed on-chip oscillator selection clock (f

SL) selection

0 Selects fSUB

Note 1

1 Selects fIL

Note 2

Notes 1. When setting f

SUB as the CPU/peripheral hardware clock, first set the SELLOSC bit to 0 and then set the CSS

bit in the CKC register to 1.

2. When setting f

IL as the CPU/peripheral hardware clock, first set the SELLOSC bit to 1 and then set the CSS

bit in the CKC register to 1.

3. When the SELLOSC bit is set to 1, the low-speed on-chip oscillator operates.

4. When setting the CKSEL register in the 20-, 30-, or 32-pin products, set the SELLOSC bit to 1.

Loading...

Loading...