RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 391

Dec 10, 2015

5.3.13 PLL Control Register (PLLCTL)

This register is used to control the PLL function. The system clock multiplied by 3, 4, 6, or 8 times or not multiplied at

all can be selected as the CPU clock and peripheral hardware clock.

Set the PLLCTL register by a 1-bit or 8-bit memory manipulation instruction.

Writing to the PLLCTL register is disabled when the GCSC bit of the IAWCTL register is set to 1.

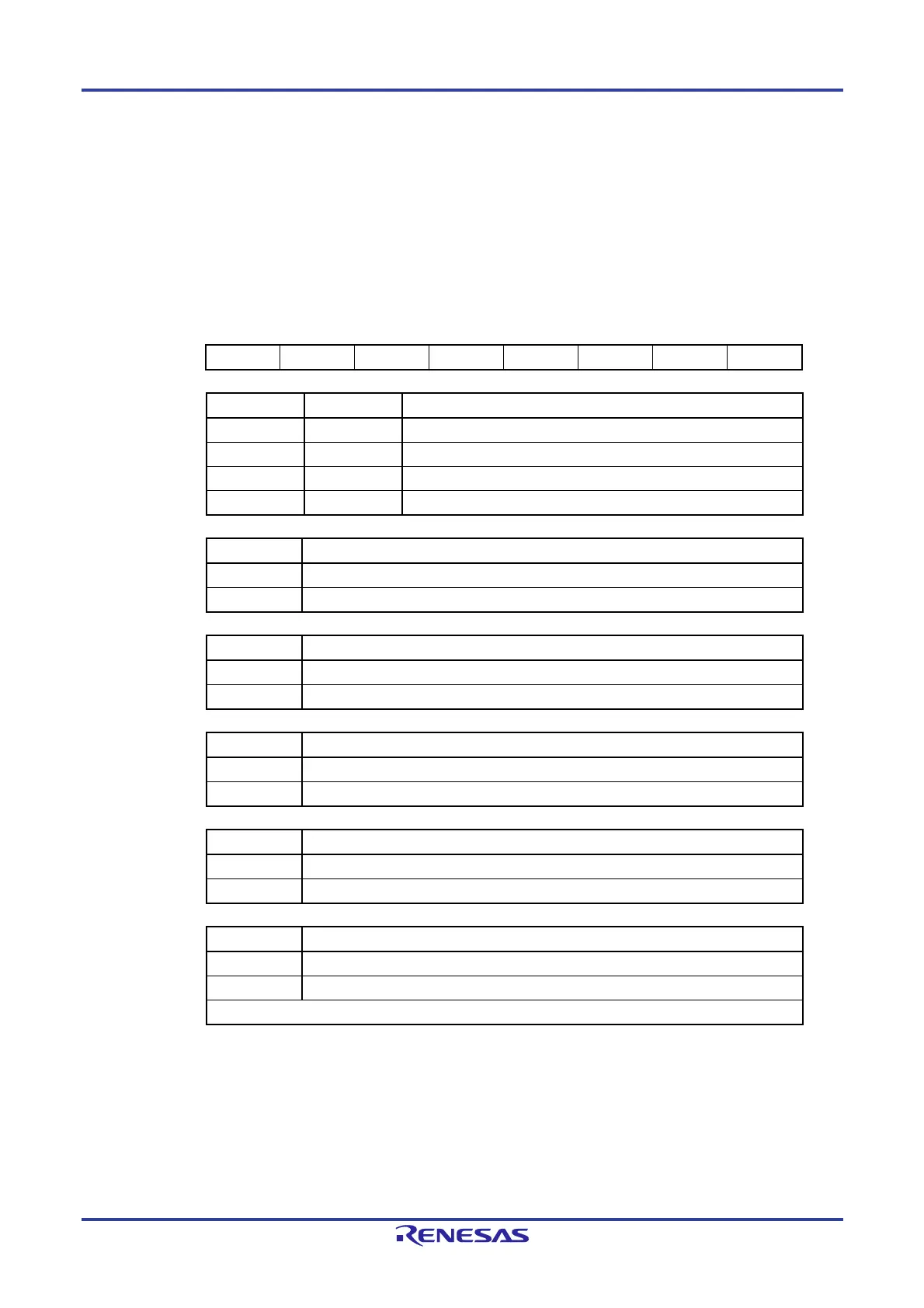

Figure 5-20. Format of PLL Control Register (PLLCTL)

Address: F02C5H After reset: 00H R/W

Symbol <7> <6> <5> <4> 3 <2> <1> <0>

PLLCTL LCKSEL1 LCKSEL0 PLLDIV1 PLLDIV0 0 SELPLL PLLMUL PLLON

LCKSEL1 LCKSEL0 Control of setting lock-up wait counter

0 0 Selects 128/fMAIN.

0 1 Selects 256/fMAIN.

1 0 Selects 512/fMAIN.

1 1 Setting prohibited

PLLDIV1 Control of PLL output clock selection

0 When fPLL 32 MHz

1 When fPLL 32 MHz

PLLDIV0 Control of PLL division selection

0 Divides the clock frequency by 2.

1 Divides the clock frequency by 4.

SELPLL Control of clock mode selection

0 Clock through mode (fMAIN)

1 PLL-clock-selected mode (fPLL)

PLLMUL Control of PLL multiplication selection

0 Multiplies the clock frequency by 12.

1 Multiplies the clock frequency by 16.

PLLON Control of PLL operation

0 Stops PLL operation.

1 Starts PLL operation.

After PLL operation starts, the lock-up wait time for frequency stabilization is required.

Cautions 1. Writing to the SELPLL bit is disabled when the PLL output is not stable (LOCK bit of

the PLLSTS register = 0).

2. When the clock monitor detects that the main system/PLL select clock has been

stopped, the SELPLL bit is not automatically cleared.

3. When the clock monitor detects that the main system/PLL select clock has been

stopped, the SELPLLS bit in the PLLSTS register is automatically cleared.

Loading...

Loading...